一文搞懂0.1UF和10UF电容并联使用技巧

摘要:搞电子的不知道小伙伴有没有被问到过,芯片附近放置的电容是多少?当你回答说是0.1uF,当你心里暗自庆幸还好自己知道的时候,面试官突然又问道为什么选取0.1uF?想必此时不少小伙伴都会想到,我看别人都是这么画的,官方推荐也是这么干的,如果你是这么回答,那面试官是不会满意的。

怎么回答才算是牛X呢?电路设计的每一个器件可以说是都不是没有根据的随便选型,只是可能到你手里之后,已经经过多方验证,是成型的原理图,参数不需要修改,所以关注的也少。回归正题,接下来分析分析,上面提到的,为什么是0.1uF电容,而不是1uF、10uF......

一、电容模型本质

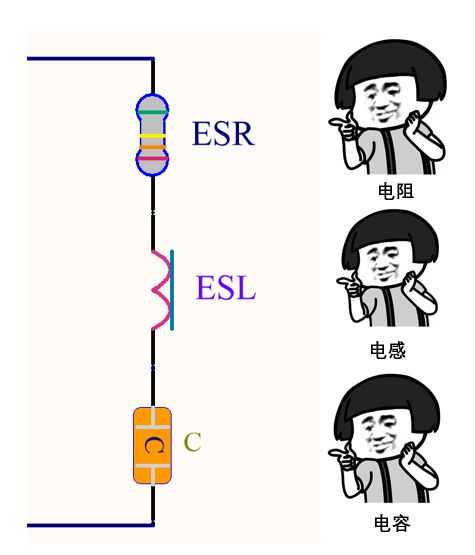

先来看看电容,电容的作用简单的说就是存储电荷。我们都知道在电源中要加电容滤波,在每个芯片的电源脚放置一个0.1uF的电容去耦。等等,怎么我看到有些板子芯片的电源脚旁边的电容是0.1uF的或者0.01uF的,有什么讲究吗。要搞懂这个道道就要了解电容的实际特性。理想的电容它只是一个电荷的存储器,即C。而实际制造出来的电容却不是那么简单,分析电源完整性的时候我们常用的电容模型如下图所示。

果果小师弟original

果果小师弟original

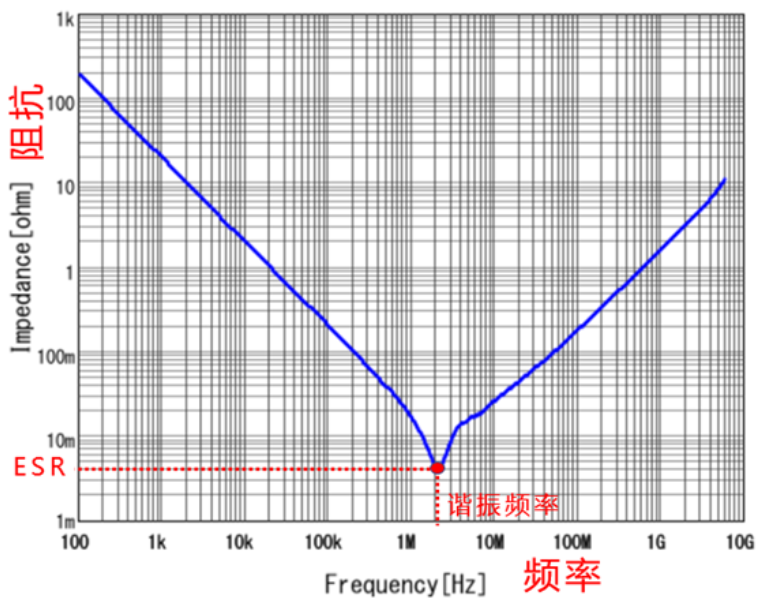

图中ESR是电容的串联等效电阻,ESL是电容的串联等效电感,C才是真正的理想电容。ESR和ESL是由电容的制造工艺和材料决定的,没法消除。那这两个东西对电路有什么影响。ESR影响电源的纹波,ESL影响电容的滤波频率特性。

电容的容抗

电感的感抗

实际电容的复阻抗为

可见当频率很低的时候是电容起作用, 而频率高到一定的时候电感的作用就不可忽视了,再高的时候电感就起主导作用了。电容就失去滤波的作用了。所以记住,高频的时候电容就不是单纯的电容了。

电容阻抗-频率曲线图

电容阻抗-频率曲线图

二、旁路和去耦

旁路电容(Bypass Capacitor)和去耦电容(Decoupling Capacitor)这两个概念在电路中是常见的,但是真正理解起来并不容易。要理解这两个词汇,还得回到英文语境中去。

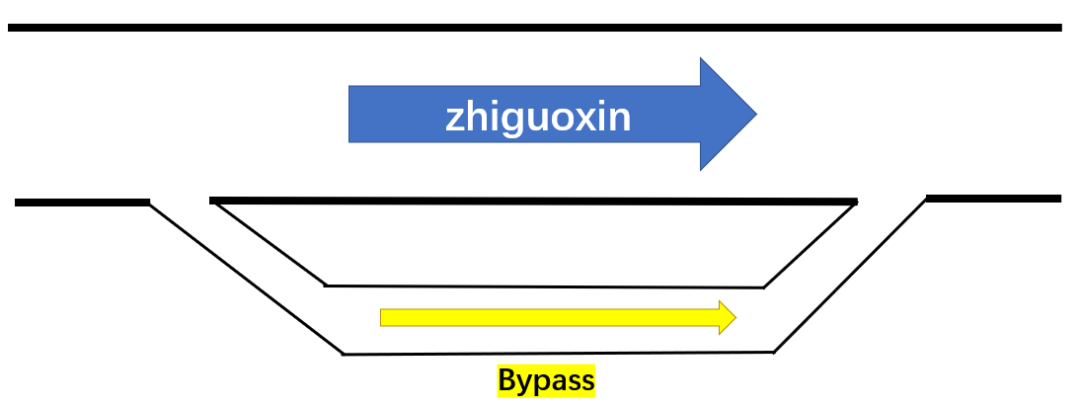

1、Bypass

Bypass在英语中有抄小路、旁路的意思,在电路中也是这个意思,如下图所示。

果果小师弟original

果果小师弟original

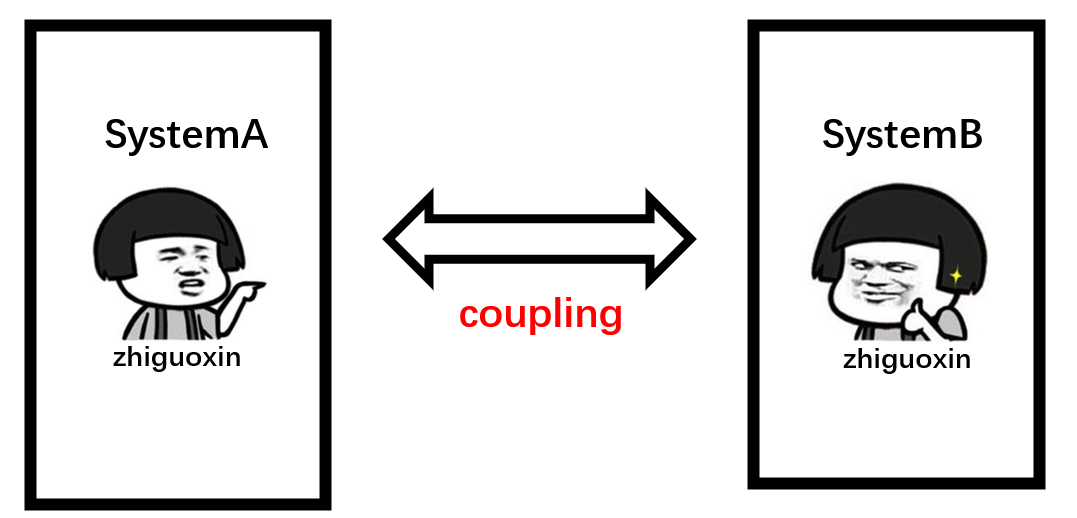

couple在英语中是一对的意思,引申为配对、耦合的意思。如果系统A中的信号引起了系统B中的信号,那么就说A与B系统出现了耦合现象(Coupling),而Decoupling就是减弱这种耦合的意思。

2、Decoupling

Couple 一对,一双。动词引申为配对,连接的意思。如果系统A中出现的事物(信号)引起了系统B中一事物(信号)的出现,或者反过来,那么我们就说系统A与系统B出现了耦合(Coupling)。Decoupling退耦即减弱这种耦合。

果果小师弟original

果果小师弟original

三、电路中的旁路和去耦

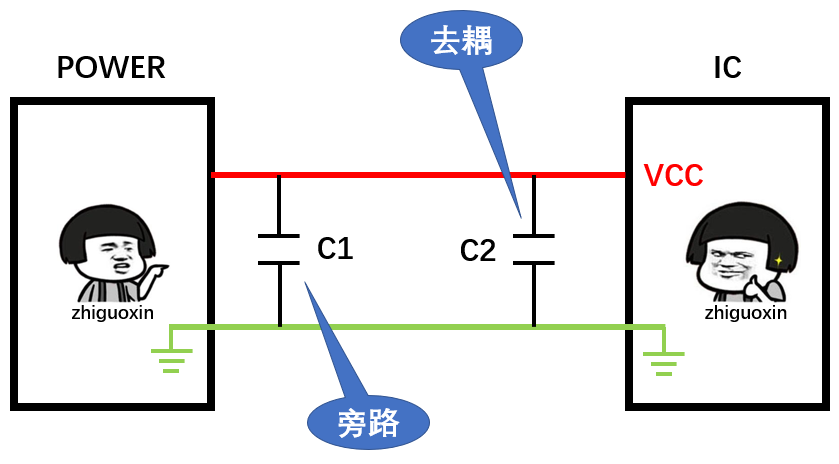

如下图中,直流电源Power给芯片IC供电,在电路中并入了两个电容。

果果小师弟original

果果小师弟original

1、旁路

如果Power受到了干扰,一般是频率比较高的干扰信号,可能使IC不能正常工作。

在靠近Power处并联一个电容C1,因为电容对直流开路,对交流呈低阻态。

频率较高的干扰信号通过C1回流到地,本来会经过IC的干扰信号通过电容抄近路流到了GND。这里的C1就是旁路电容的作用。

2、去耦

由于集成电路的工作频率一般比较高,IC启动瞬间或者切换工作频率时,会在供电导线上产生较大的电流波动,这种干扰信号直接反馈到Power会使其产生波动。

在靠近IC的VCC供电端口并联一个电容C2,因为电容有储能作用,可以给IC提供瞬时电流,减弱IC电流波动干扰对Power的影响。这里的C2起到了去耦电容的作用。

四、为什么要用2个电容

回到本文最开始提到的问题,为什么要用0.1uF和0.01uF的两个电容?

电容阻抗和容抗计算公式分别如下:

容抗与频率和电容值成反比,电容越大、频率越高则容抗越小,对交流电的阻碍作用就越小。可以简单理解为电容越大,滤波效果越好。那么有了0.1uF的电容旁路,再加一个0.01uF的电容不是浪费吗?

实际上,对一个特定电容,当信号频率低于其自谐振频率时呈容性,当信号频率高于其自谐振频率时呈感性。当用0.1uF和0.01uF的两个电容并联时,相当于拓宽了滤波频率范围。

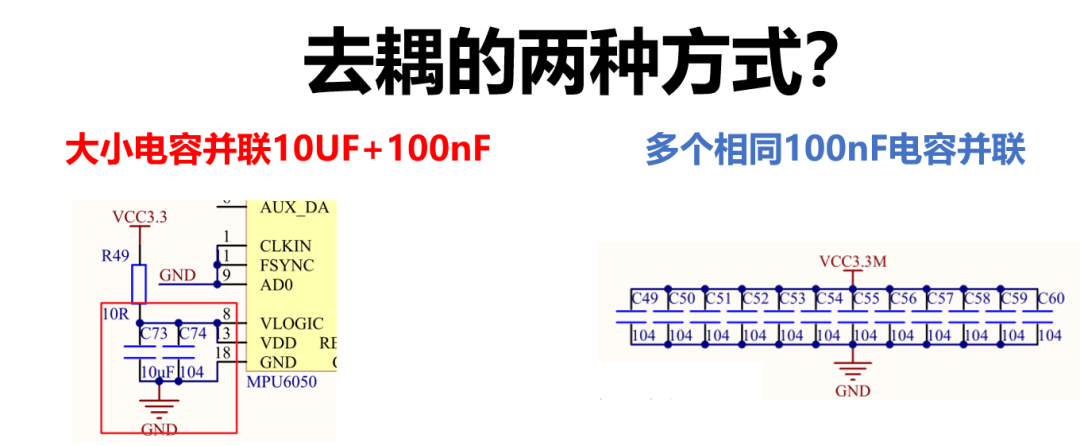

两种方式组合滤波

实际电路中我们需要去耦的频率范围会比较宽,因此一个电容搞不定,那怎么办呢?我们经常有两种方法来解决,一种是使用一个大电容和一个小电容并联,还有一种是使用多个相同的电容并联。

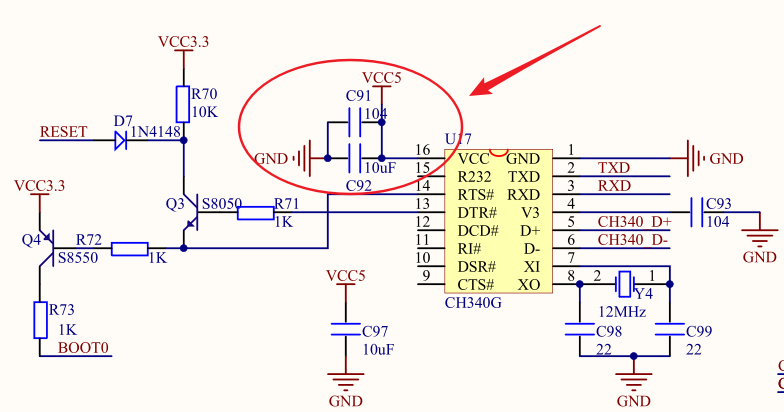

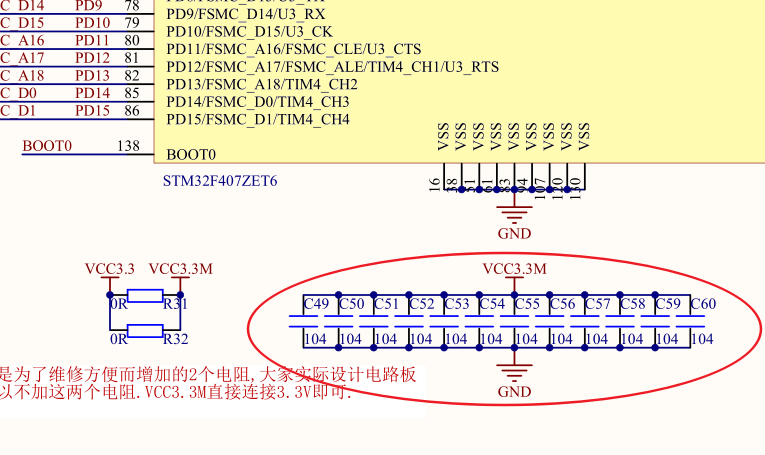

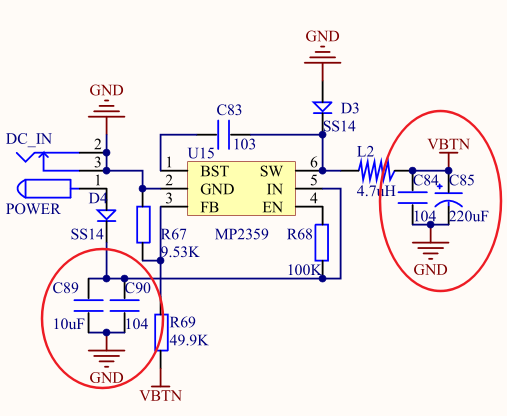

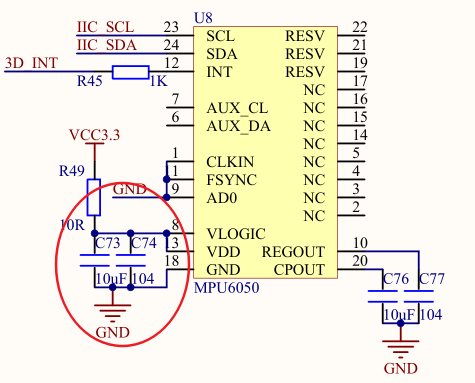

以下是正点原子开发板上面的一些模块芯片的电路,可供参考。

CH340 CH340 |

STM32 STM32 |

MP2359 MP2359 |

MPU6050 MPU6050 |

五、电容选型建议

| 频率范围/HZ | 电容取值(智果芯) |

|---|---|

| DC-100K | 10uF以上的钽电容或铝电解 |

| 100K-10M | 100nF(0.1uF)陶瓷电容 |

| 10M-100M | 10nF(0.01uF)陶瓷电容解 |

| 100M以上 | 1nF(0.001uF) 陶瓷电容和PCB的地平面与电源平面的电容解 |

所以,以后不要见到什么都放0.1uF的电容,有些高速系统中这些0.1uF的电容根本就起不了作用。

—— The End ——

文章来源: great.blog.csdn.net,作者:小麦大叔,版权归原作者所有,如需转载,请联系作者。

原文链接:great.blog.csdn.net/article/details/121155170

- 点赞

- 收藏

- 关注作者

评论(0)