计算机组成原理重难点2:存储器与CPU的连接

有需要的可以订阅我的专栏获取更多计算机组成原理相关知识,内涵期末考试总结、必备概念解析、重难点讲解、考研习题等等。

计算机组成原理专栏

存储容量的扩展

由于单片存储芯片的容量总是有限的,很难满足实际的需要,因此,必须将若干存储芯片连在一起才能组成足够容量的存储器,称为存储容量的扩展,通常有位扩展和字扩展。

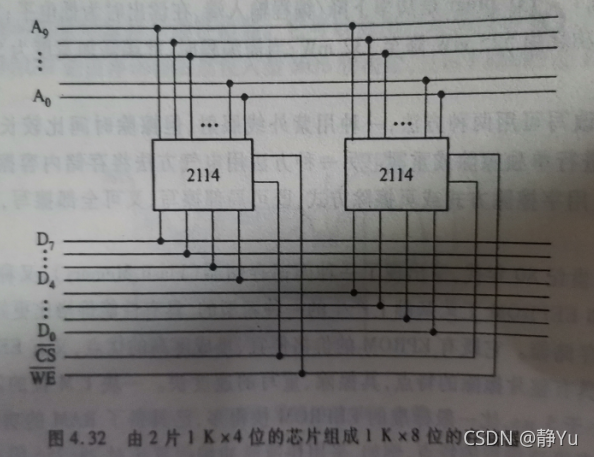

(1)位扩展

位扩展是指增加存储字长。

例如:2片1K×4位的芯片可组成1K×8位的存储器

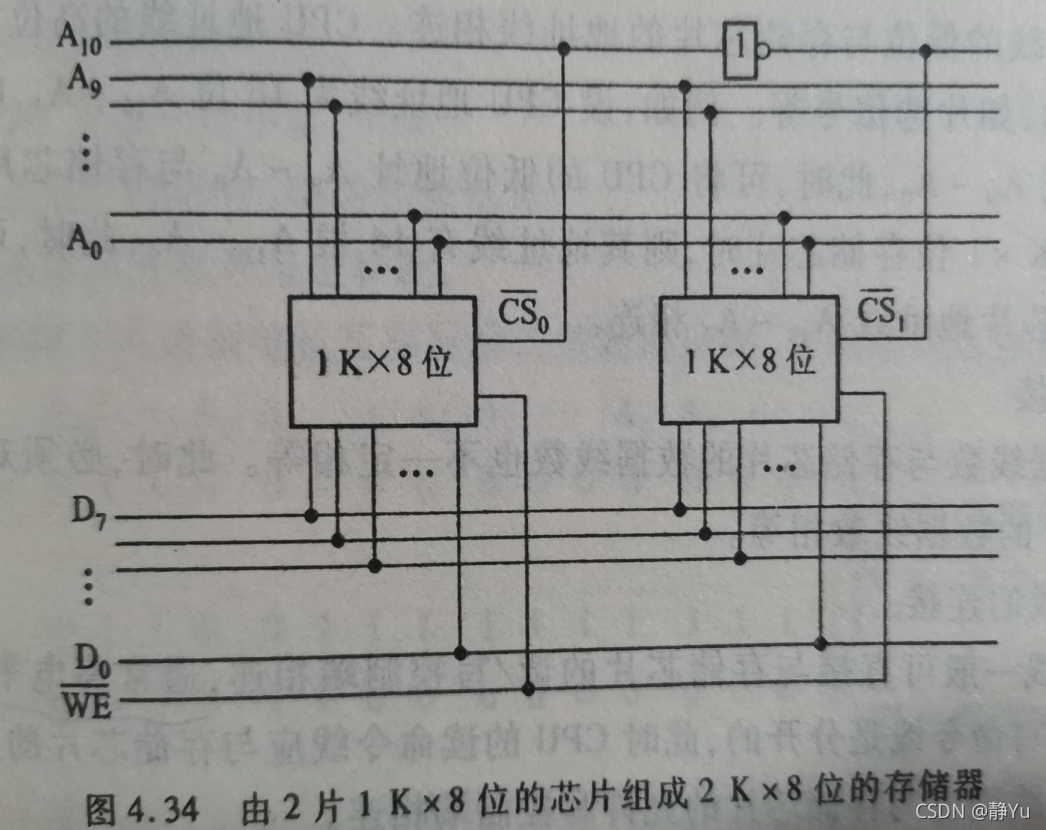

(2)字扩展

字扩展是增加存储器字的数量。

例如:2片1K×8位的存储芯片可组成2K×8位的存储器。

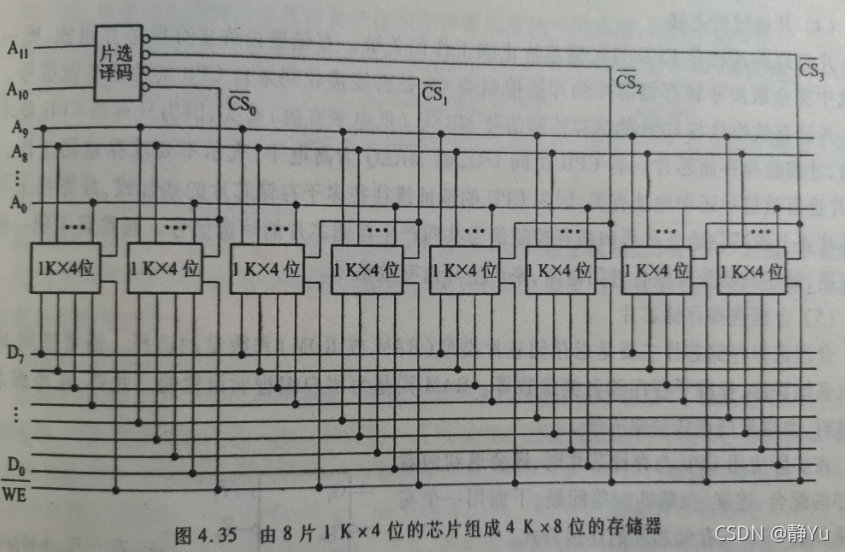

(3)字、位扩展

字、位扩展是指即增加存储字的数量又增加存储字长。

例如:8片1K×4位的芯片可组成4K×8位的存储器。

存储器与CPU芯片的连接

存储芯片与CPU芯片相连时,特别注意片与片之间的地址线、数据线和控制线的连接。

(1)地址线的连接

通常情况是将CPU地址线的低位与存储芯片的地址线相连。CPU地址线的高位或在存储芯片扩充时用,或做其它用途,入片选信号。

例如:16K×1位存储芯片连接时,地址线有14根与CPU相连。

(2)数据线的连接

CPU的数据线数与存储芯片的数据线数也不一定相等。此时必须对存储芯片扩展。使其数据位数与CPU的数据线相等。

(3)读/写命令线的连接

CPU读/写命令线一般可直接与存储芯片的读/写控制端相连,通常高电平为读,低电平为写。

(4)片选线的连接

存储器由许多存储芯片组成,哪一片被选中完全取决于该存储芯片的片选控制端CS非能否收到来自CPU的片选有效信号。

片选有效信号与CPU的访存控制信号MREQ非(低电平有效)有关,因为只有当CPU要求访存时,才需要选择存储芯片。若CPU访问I/O时,则MREQ非为高电平,表示不要求存储器工作。

例题

设CPU有16根地址线、8根数据线,并用MREQ非作为访存控制信号(低电平有效),用WR非作为读/写控制信号(高电平为读,低电平为写)。现有下列存储芯片:1K×4位RAM、4K×8位RAM、8K×4位RAM、2K×8位ROM、4K×8位ROM、8K×8位ROM及74138译码器和各种门电路。

画出CPU与存储器的连接图。

解题步骤:

1.主存地址空间分配:

6000H~67FFH为系统程序区

6800H~6BFFH为用户程序区

2.合理选用上述存储芯片,说明各选几片

3.详细画出存储芯片的片选逻辑图

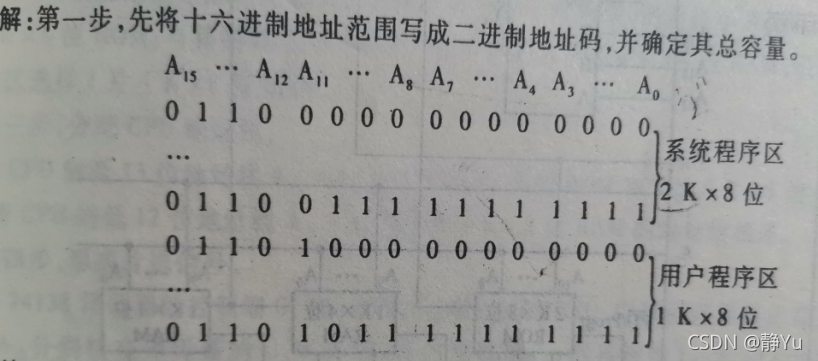

第一步:

第二步:

根据地址范围的容量以及该范围在计算机系统中的作用,选择存储芯片。

根据6000H~ 67FFH为系统程序区的范围,应选择1片2Kx8位的ROM,若选择4Kx8位或8Kx8位的ROM、都超出了2 K x8位的系统程序区范围。

根据6800H ~ 6BFFH为用户程序区的范围,选2片1 Kx4位的RAM芯片正好满足1 Kx8位的用户程序区要求。

第三步:

分配CPU的地址线。

将CPU的低11位地址A10~A0与2Kx8位的ROM地址线相连;将CPU的低10位地址A9-A0与2片1Kx4位的RAM地址线相连。剩下的高位地址与访存控制信号MREQ非共同产生存储芯片的片选信号。

第四步:

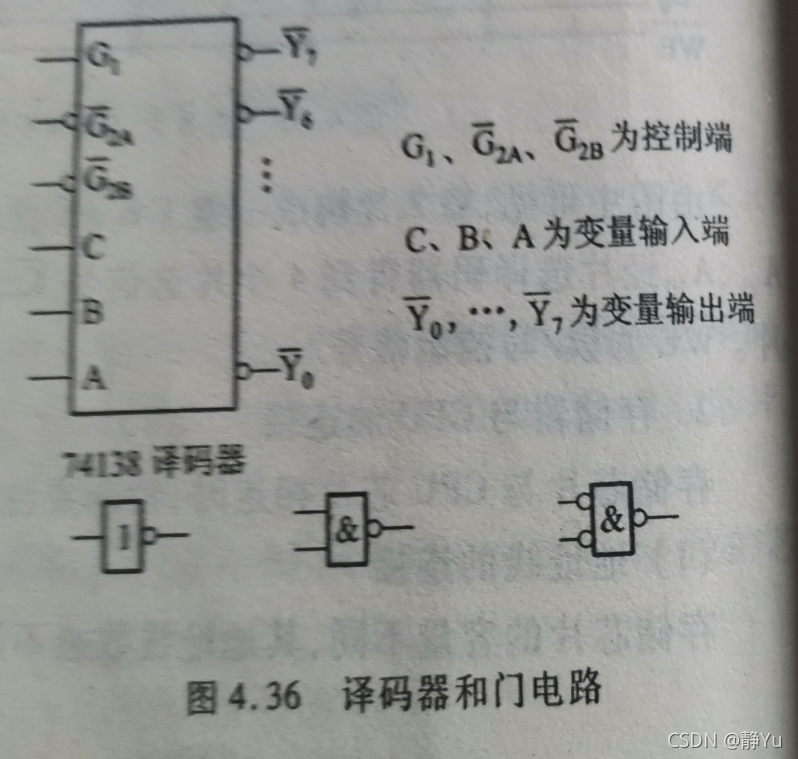

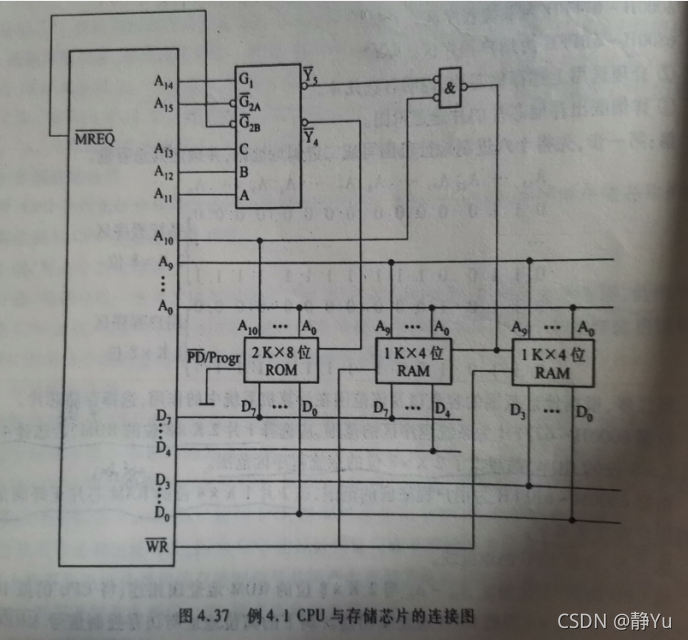

由图4.36给出的74138译码器输入逻辑关系可知,必须保证控制端G1为高电平,G2与G23为低电平,才能使译码器正常工作。

根据第一步写出的存储器地址范围得出,A15始终为低电平,A14始终为高电平,它们正好可分别与译码器的G2A(低)和G1(高)对应。

而访存控制信号MREQ非(低电平有效)又正好可与G2B(低)对应。 剩下的A13、A12、A11可分别接到译码器的C、B、A输人端。其输出Y4有效时,选中1片ROM;Y5与A10同时有效均为低电平时, 与门输出选2片RAM,如图4.31所示。图中ROM芯片的PD/progr端接地,以确保在读出时低电平有效。

RAM芯片的读写控制端与CPU的读写命令端WR相连。ROM的8根数据线直接与CPU的8根数据线相连,2片RAM的数据线分别与CPU数据总线的高4位和低4位相连。

- 点赞

- 收藏

- 关注作者

评论(0)