apollo系列之apollo2 mcu开发(基础篇)之1.2-apollo2 mcu core

查看全部教程开发请点击:apollo系列汇总

查看本文全部文章请点击:apollo系列之apollo2 mcu开发(基础篇)之1.2-apollo2 mcu core

====================================================================

版权归作者所有,未经允许,请勿转载。

====================================================================

Apollo2 MCU的核心是一个32位的ARM Cortex-M4内核,带有浮点选项。ARM v7-M体系结构的3个阶段的流水线实现以非常低的功耗设计提供了高效的处理。ARM M DAP通过串口线接口从外部打开调试访问允许访问所有的内存和外围设备的MCU。

一、Apollo2 MCU 低功耗模式

- 活动模式

- 休眠模式

- 深度模式

- 关机

二、中断事件有哪些呢?

- NVIC

- 唤醒中断控制器

- 退出休眠

- 进入休眠,等待中断

在MCU中,多个外设可以产生中断。在某些情况下,单个外围设备可能会产生多个不同的中断。由外设产生的每个中断信号都被连接回M4核心在两个方面:

首先,在内核中断连接到嵌套的矢量中断控制器,NVIC;此连接提供了与中断处理相关的程序流的标准更改。

此外,它们连接到核心外部的WIC,允许中断源在M4核心处于深度睡眠(SRP)时唤醒它。

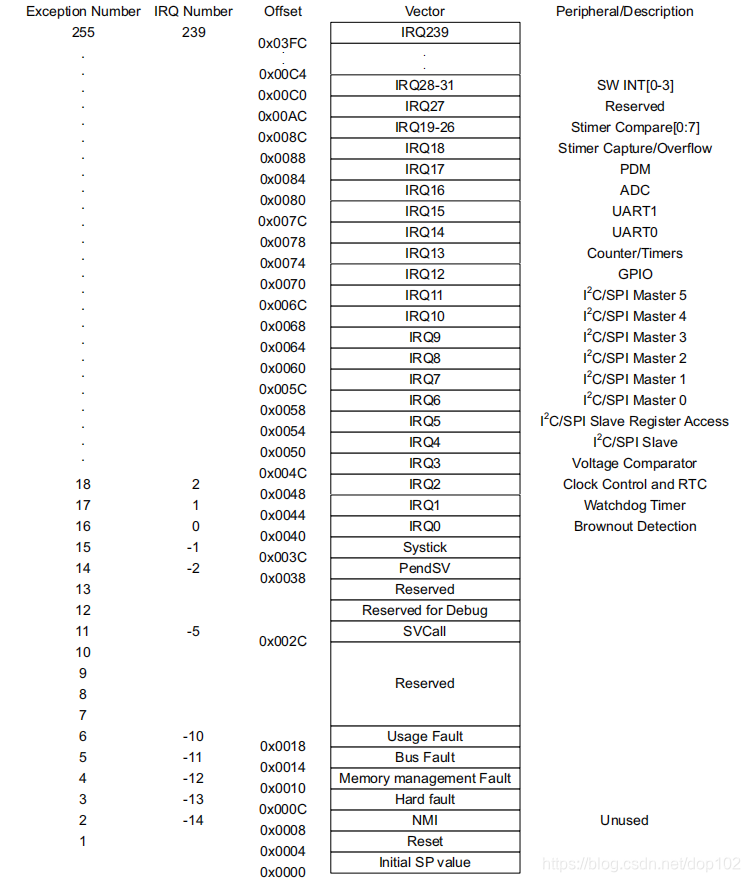

Apollo2单片机的M4矢量表:

Cortex-M4允许用户根据应用程序的要求将各种中断分配到不同的优先级级别。在apollo2 mcu实现中,有8种不同的优先级。

M4中断架构的另一个特性是能够将向量表重新定位到一个不同的地址。如果应用程序的特定模式需要一组不同的中断服务例程,那么这可能很有用。软件可以将矢量表移动到SRAM中,并根据需要重新分配中断服务程序入口地址。

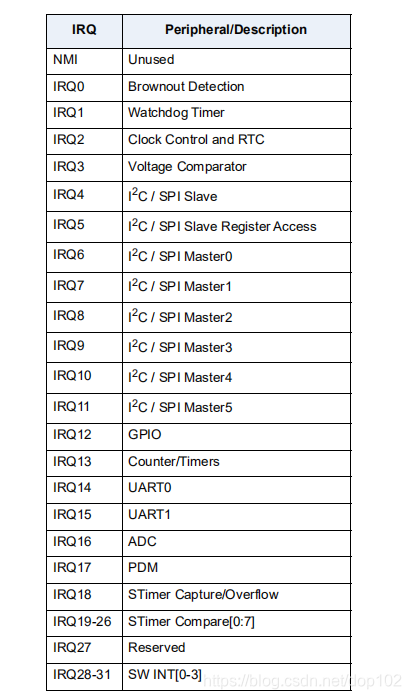

如下所示,硬件中断在MCU中分配给M4 NVIC。

三、内存映射

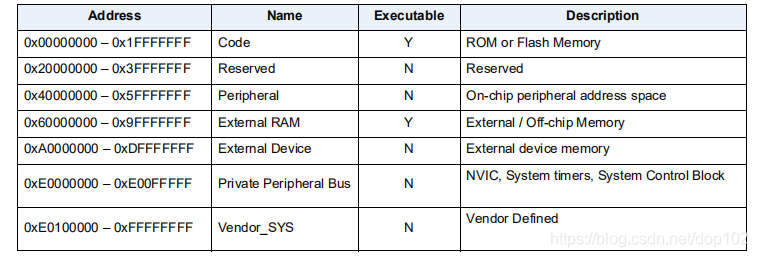

ARM为基于ARM v7-M架构的设备提供了定义良好的内存映射。M4进一步细化了外围设备和系统地址范围的地图。下面是ARM定义的系统内存映射

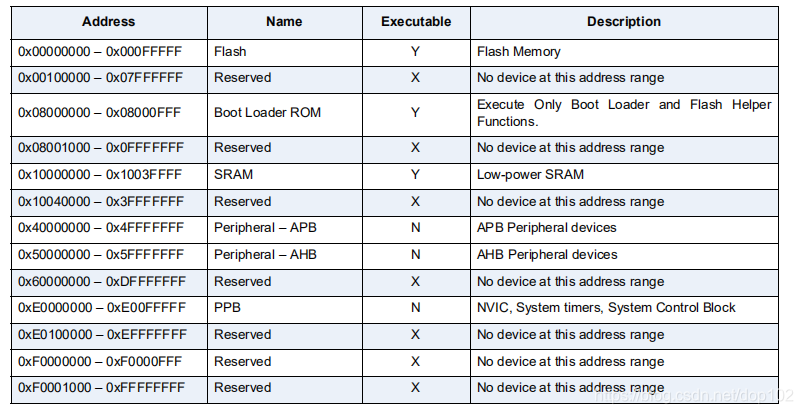

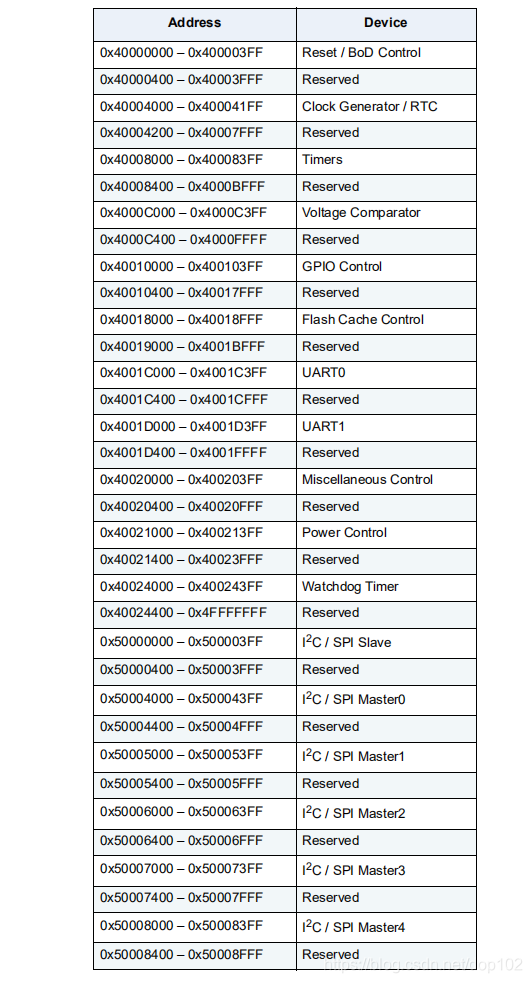

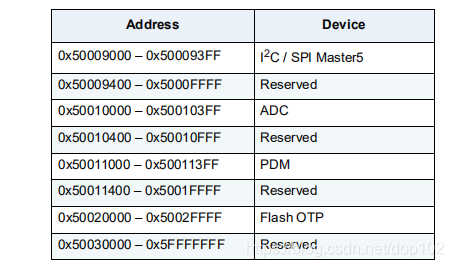

该内存映射的mcu具体实现如下:

内存映射中的外围设备在4 KB的边界上分配,允许每个设备最多1024个32位控制和状态寄存器。当试图访问不存在的寄存器时,外设将返回未定义的读数据。外设,无论是通过APB还是AHB访问,都将始终接受发送到其寄存器的任何写数据,而不会尝试返回错误响应。具体地说,对只读寄存器的写操作将变成无关紧要的写操作。

单片机外围设备内存映射:

四、MPU

Apollo2单片机包括一个主控板,主控板是内存保护的核心部件。M4处理器支持标准的ARMv7保护内存系统架构模型。MPU提供全面支持:

- 保护区域。

- 重叠的保护区域,区域优先级上升:- 7 =最高优先级- 0 =最低优先级。

- 访问权限

- 导出内存属性到系统。

你可以使用MPU来:

▪执行特权规则。

▪独立的进程。

▪强制执行访问规则。

五、系统总线

ARM Cortex-M4利用AMBA AHB总线的3个实例与存储器和外设通信。代码总线被设计用来从“代码”内存空间获取指令DCode总线是为同一区域的数据和调试访问而设计的。设计了系统总线,用于读取SRAM和其他单片机的外围设备。

Apollo2 MCU将可用SRAM内存映射到“代码”内存空间中的地址空间。这使用户有机会从较低的功率执行指令和数据获取SRAM有效降低了单片机的功耗。

Apollo2单片机的外围设备很少被访问,它们位于AMBA APB总线上。存在一个桥接器,将系统AHB的访问转换到APB。在任何访问周期中,对这些外设的访问都将在AHB上注入一个单一的等待状态。

六、电源管理

电源管理单元(PMU)是一种有限状态机,它控制MCU在不同电源模式之间的转换。当从主动模式移动到深度睡眠模式,PMU管理在Cortex-M4核心内寄存器的状态保持能力,并控制关闭单片机的电压调节器。一旦进入深度睡眠模式,PMU,连同唤醒

中断控制器,等待一个唤醒事件。当事件被观察到,PMU通过重新使能片上电压调节器和恢复CPU寄存器状态开始电源恢复过程。的M4然后返回到活动模式,一旦所有的状态就绪。

6.1 Cortex-M4电源模式

活动模式

休眠模式

深度休眠模式

除了上述arm定义的模式外,Apollo2 MCU将支持整个设备断电的关机模式,但支持上电复位所需的逻辑除外。

每种模式如下所述。

6.1.1 活动模式

在Active模式下,M4被上电,时钟被激活,指令被执行。在这种模式下,M4期望连接到AHB和APB的所有(启用的)设备为正常访问供电和时钟。所有非调试的ARM时钟(FCLK, HCLK)在这个状态下都是活动的。

为了从主动模式转换到任何低功耗模式,在M4核心上执行特定的指令序列。首先,必须设置ARMv7-M系统控制寄存器中的特定位来确定要进入的模式。请参阅ARMv7-M架构参考手册B3-269页。

设置好SCR后,代码可以通过以下两种方法之一进入低功耗状态:

- 执行一个WFI指令。

- 设置SCR的SLEEPONEXIT位,这样ISR的退出将自动返回到睡眠状态。

M4将进入一个低功率模式后,其中一个执行(假设所有条件都满足),并保持那里,直到一些事件导致核心返回活动模式。返回活动模式的可能原因是:

- 重置

- NVIC接收到一个启用的中断

- 从DAP收到一个调试事件

6.1.2 休眠模式

在睡眠模式,M4是通电的,但时钟(HCLK, FCLK)是不活跃的。电源仍然应用到M4逻辑,这样它可以立即成为活跃的唤醒事件,并开始执行指令。

6.1.3 深度休眠模式

在深度睡眠模式下,M4进入SRPG模式,主电源被移除,但flops保持其状态。时钟不激活,HCLK和FCLK的MCU时钟源可以去激活。为了方便移除源电源和进入SRPG模式,M4将与唤醒中断控制器和电源管理单元握手,并设置可能的唤醒条件。

6.2 系统电源模式

6.2.1 SYS Active Burst

6.2.1 SYS Active

6.2.3 SYS Sleep Mode 0

6.2.4 SYS Sleep Mode 1

6.2.5 SYS Deep Sleep Mode 0

6.2.6 SYS Deep Sleep Mode 1

6.2.7 SYS Deep Sleep Mode 2

6.2.8 SYS Deep Sleep Mode 3

6.2.9 SYS OFF Mode

文章来源: xintiaobao.blog.csdn.net,作者:心跳包,版权归原作者所有,如需转载,请联系作者。

原文链接:xintiaobao.blog.csdn.net/article/details/112588049

- 点赞

- 收藏

- 关注作者

评论(0)