让你忍不住想要动手收藏的—计算机组成原理总结

还会持续更新

转载说明:务必注明来源,附带本人CSDN博客连接。

关注公众号:神的孩子都在歌唱 回复:组成原理 获取pdf电子版

@TOC

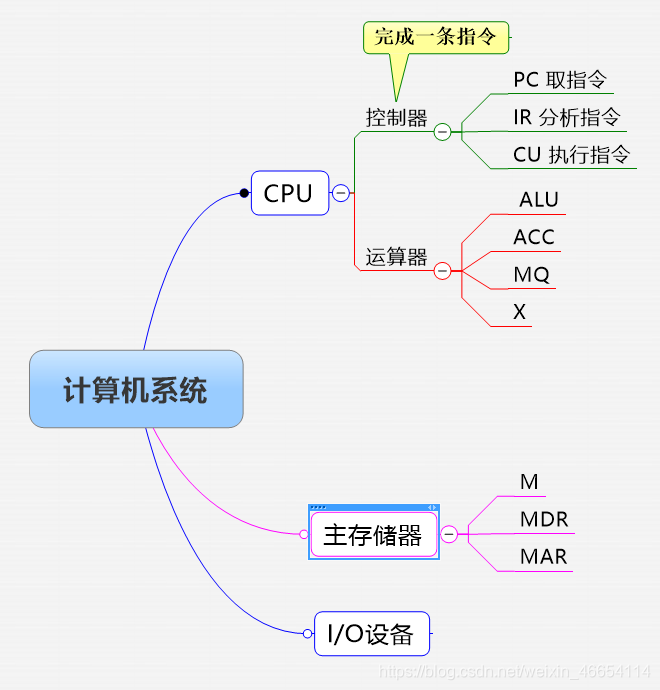

第1章:计算机的系统

硬件:指计算机实体部分。(看得见摸得着的)

软件:通过编译具有各类特殊功能的程序组成(看不见摸不着)

冯.诺依曼计算机:以运算器为中心

现代计算机:以存储器为中心

1.计算机由运算器,存储器,控制器,输入,输出设备过构成。

2.现代计算机三大组成:CPU,I/O设备,主存储器

3.工作步骤:(1)建立数学模型 (2)确定计算方法(3)编制解题程序

4.存储容量=存储单元个数(MAR 1k=1024=2^10)x存储字长(MDR 1M=2 ^20)

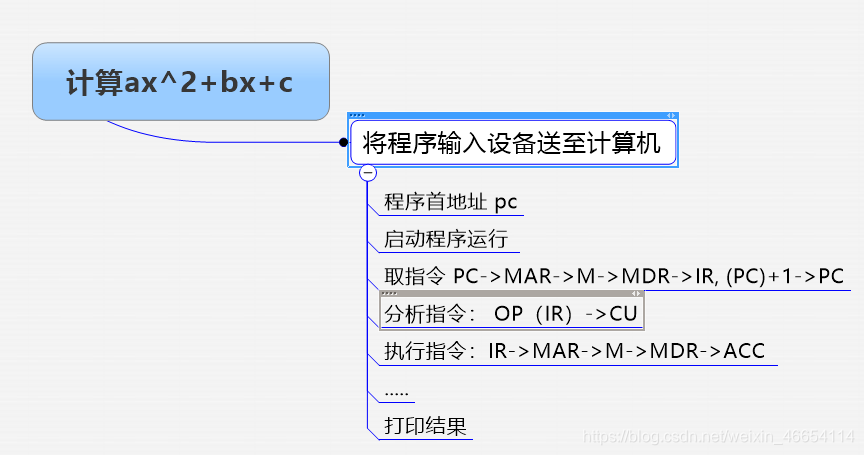

ax^2+bx+c在计算机中的运行过程

各种英文代号解释

CPU:(Central Processing Unit)中央处理器

I/O设备:(Input/Output Equip-ment)输入,输出设备

MM: (Main Memory)主存储器

ALU: (Arithmetic Logic Unit)算数逻辑单元

ACC:(Accumulator)累加器

MQ:(Multiplier-Quotient Register)乘商寄存器

X:操作数寄存器

PC:(Program Counter)程序计数器

IR:(Instruction Register)指令寄存器

CU:(Control Unit)控制单元

MAR:(Memory Address Register)存储器地址寄存器,反映单元个数

MDR:(Memory Data Register)存储器数据寄存器,反映字长

第3章:系统总线

总线是信号的公共传输线,是连接多个部件的信息传输线,是各部件共享的传输介质。

发展过程:

- 面向CPU的双总线:这种结构在I/O设备与主存交换信息是仍然要占用CPU,因此还会影响CPU的工作效率。

- 单总线结构(系统总线):只有一组总线,当都要占用总线时,就会发生冲突。

- 以存储器为中心的双总线结构:由单总线基础上,在CPU与主存之间连接一条存储总线。

分类:

- 片内总线:芯片内部的线。

- 系统总线:计算机各部件之间的信息传输线。

(1)数据总线(双向):传输数据信息。位数与机器字长,存储字长有关,是衡量性能重要参数。

(2)地址总线(单向):指出在数据总线上==数据==在主存单元或I/O设备的地址,地址线的位数与存储单元的个数有关

(3)控制总线(单向,双向):发出各种控制信号,监视各部件状态。 - 通信总线:用于计算机系统之间或计算机系统与其他系统(外部系统) 传输方式:==串行通信,并行通信==

特性:

- 机器特性

- 电气特性

- 功能特性

- 时间特性

性能指标:

- 总线宽度:指数据总线的根数,用bit(位)表示,如8位(8根)。

- 总线带宽(数据传输速率):既单位时间内总线上传输数据的位数,用每秒传输信息的字节数来衡量,单位用MBps(兆字节每秒)。

- 时钟同步/异步:数据与时钟。

- 总线复用:地址线和数据线的复用。

- 信号总线:三种总线的总和。

判优控制

- ==主设备==对总线有控制权,==从设备==只能响应从设备发来的总线命令

- 判优控制可分为==集中式==和==分布式==。

集中控制优先权仲裁方式:

(1)链式查询:控制线少,对电路故障敏感,优先级低的设备难请求

(2)计数器定时查询:控制复制

(3)独立请求方式:响应快,优先次序控制灵活

通信控制

- 总线周期:完成一次总线操作的时间。

- 目的:解决通信双方如何协调配合。

- 方式:

(1)同步通信:通信双方由统一时标。

(2)异步通信:采用应答方式,没有公共时钟标准。

(3)半同步通信:同步,异步结合。

(4)分离式通信:充分挖掘系统总线每个瞬间的潜力。

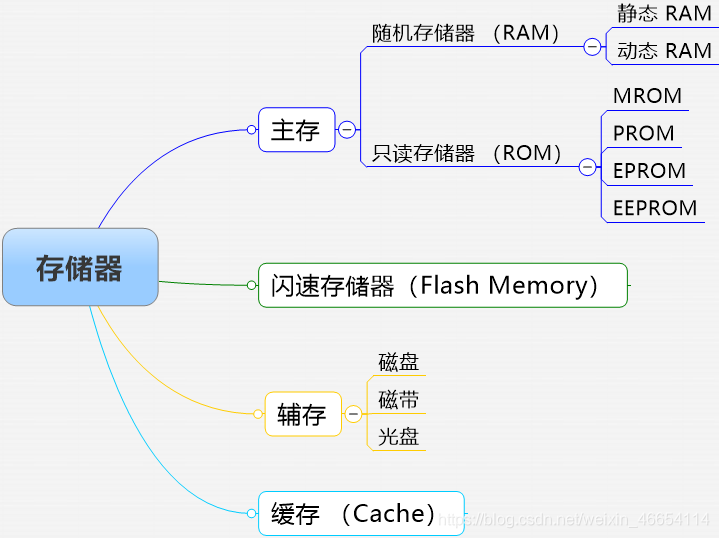

第4章:存储器

一. 概述

分类:

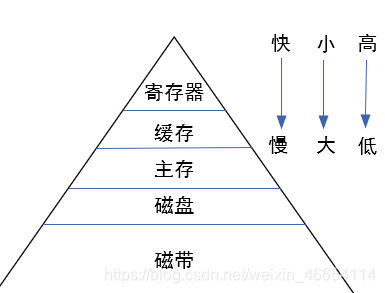

层次结构:

- 性能指标:速度,容量,位价(每位价格)。

- 存储层次结构:

(1)缓存-主存层次:解决==CPU==和==主存速度==不匹配问题。

(2)主存-辅存层次:解决容量问题。

二.主存储器

1.概述

- 基本组成: 存储体(大楼)–存储单元(房间)–存储元件(床位)-- 0 / 1(无人/有人)。

- 主存中存储单元地址的分配: 主存个存储单元的空间位置是由单元地址号来表示,地址总线是指出储存单元地址号,由地址号可以读出写入一个储存字。

- 技术指标:

(1)==存储容量== :指主存能存放二进制代码的总位数,也可用字节总数 来表示。

存储容量=存储单元个数 x 存储字长

存储容量=存储单元个数 x 存储字长/8

(2)==存储速度== :由存取时间和存储周期来表示。

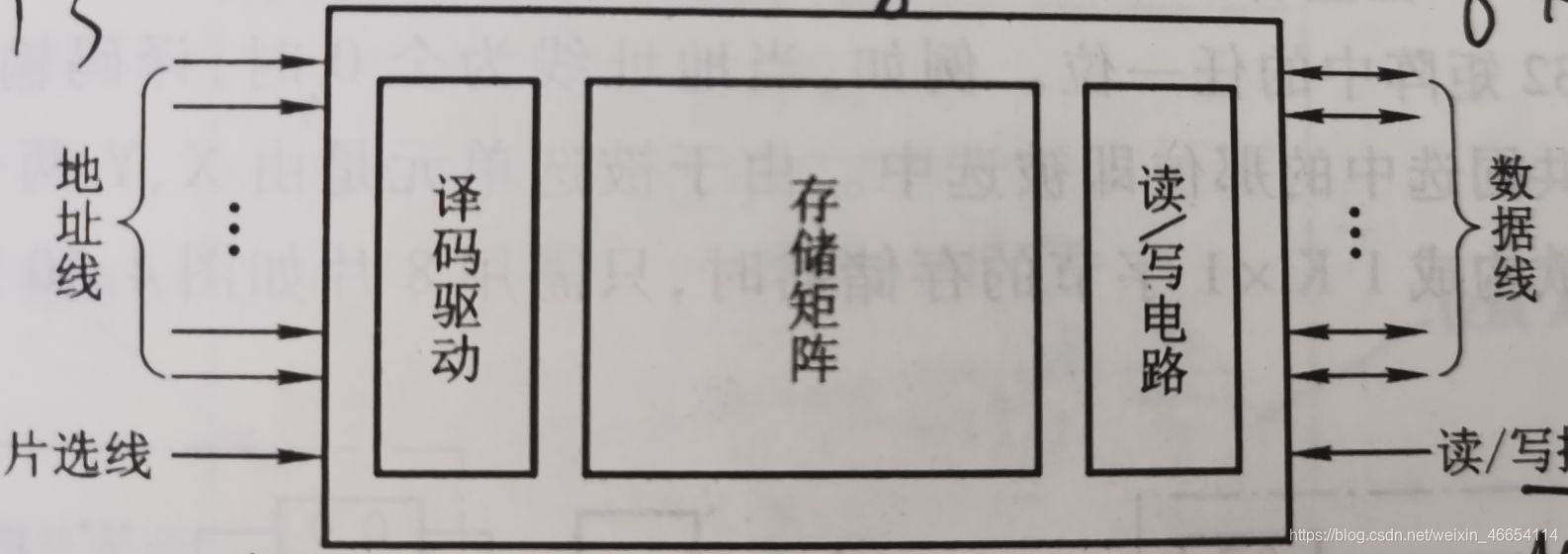

2. 半导体储存芯片

基本结构:

容量:由==地址线==(单向)和==数据线==(双向)的位数共同反应。

列:

| 地址线 | 数据线 | 容量 |

|---|---|---|

| 10 | 4 | 2^10(1k)*4 |

| 14 | 1 | 2^14(16k)*1 |

| 13 | 8 | 2^13(8k)*8 |

控制线:

(1)读写控制线:决定芯片进行读写操作。

(2)片选线:用来选择储存芯片。

译码驱动方式:==线选法==和==重合法==

3.随机存储器(RAM)

DRAM(动态):用在==主存==

SRAM(静态):用在==缓存==

| DRAM(动态) | SRAM(静态) | |

|---|---|---|

| 存储原理 | 容量 | 触发器 |

| 集成度 | 高 | 低 |

| 芯片引脚 | 少 | 多 |

| 功耗 | 小 | 大 |

| 价格 | 低 | 高 |

| 速度 | 慢 | 快 |

| 刷新 | 有 | 无 |

4.只读存储器(ROM)

定义: 一般保存系统程序或系统的配置信息

半导体ROM基本器件:MOS型和TTL型。

- MROM:用户不发改变原始状态。

- PROM:可以改变一次(一次性)。

- EPROM:(多次性编程)。

- EEPROM:既可局部,也可全部。

- 闪速存储器:快擦型存储器

5.存储器与CPU的连接

- 存储容量的扩展

CS (片选线 ):连接芯片

WE:读,写

(1)位扩展 : 指增加==存储字长==(就是增加数据线)。

(2)字扩展 :指增加==存储器字的数量==,也称存储单元(就是增加地址线)

(3)字,位扩展 :两个都增。

- 存储器与CPU连接

(1)地址线连接:通常将==CPU地址线的低位==与==存储芯片的地址线相连==(CPU地址线多于存储芯片地址线)。

(2)数据线连接 : 若存储芯片与CPU的数据线不相等,就对存储芯片进行==扩位==(使他们数据位数相等)。

(3)读 / 写命令线连接 :高电平为读,低电平为写。

(4)片选线连接 :是CPU与存储芯片正确工作的关键。==片选有效信号==与CPU的访存信号MREQ(低电平有效,有效时,这次访问的地址才在存储器当中)有关。

(5)合理选择存储芯片 :==ROM==存放系统程序,==RAM==为用户编程设计。

解题步骤

(1)写出对应的二进制地址码

(2)确定芯片数量及类型

(3)分配地址线

(4)确定片选信号

(5)确定片选逻辑

6.存储器校验

- 汉明码:1950年提出,具有以为纠错能力。

- 汉明码的分组是一种非划分方式。

- 校验位: 指对一组数据进行效验,不和其他组共有。

7.提高访存速度的措施

目的:提高主存的存取速度

多体并行系统:采用多体模块组成的存储器。

三.高速缓冲存储器(cache)

1.概述

主要作用:解决主存与CPU速度不匹配的问题。

- 工作原理

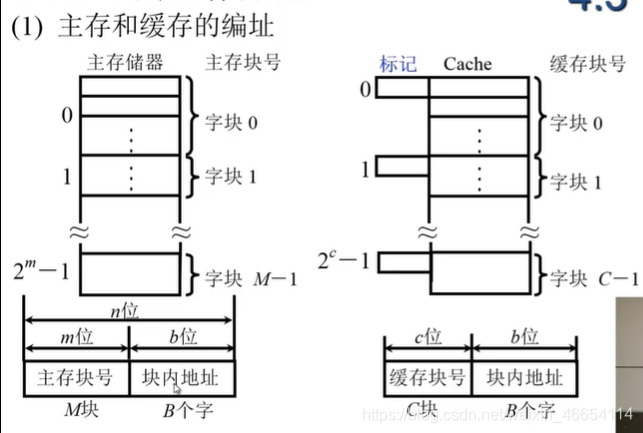

- 主存由2^n个可编译的字组成,每个字有唯一的n位地址

- ==主存== 和 ==缓存==以==块== 为单位存储。

- 块的大小相同

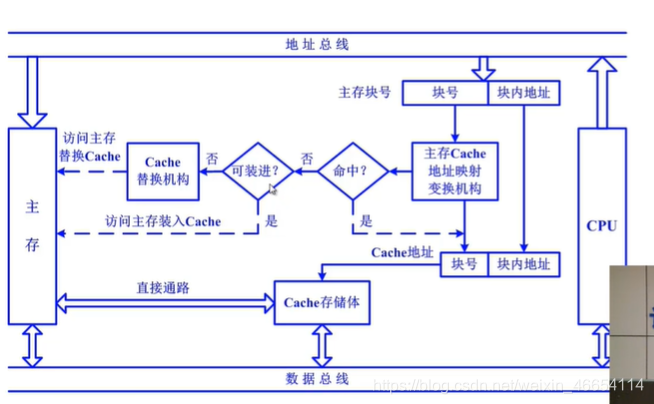

- CPU读取主存的字

两种情况(1)所需字已在缓存中,可直接访问Cache(一次送一个字节)。

(2)不在,将改字所在的主存整个字块调到缓存。 - 命中率

(1)Cache ==容量越大== CPU命中率越高。

(2)命中Cache:说明主存快已经调入缓存中。

(3)未命中:未调入。 - 基本结构

(1)Cache存储体。

(2)地址映射变换机构

(3)替换机构

(4)Cache的读写操作

2.Cache–主存地址映射和替换策略

映射机构:主存的块可以放到缓存那些块当中。

替换机构:完成了主存当中的一个块在Cache当中的查找操作。

- 直接映射(不灵活):==某一== 主存块==只能固定==映射到==某一==缓存块。

- 全相联映射(成本高):==某一==主存块==能== 映射到==任一==缓存块

- 组相联映射:==某一== 主存块==只能==映射到==某一==缓存组中的==存储块==当中

算法:

- 先进先出(First-In-First-out,FIFO)算法。

- 近期最少使用(Least Recently Used,LRU)算法。

四.辅助存储器(外部存储器)

特点:不直接与CPU交换信息

与主存一起组成了存储器系统的==主存-辅存==层次

第5章:输入输出系统

你们可能看不懂我的题目,那么接下来跟我一起去了解输入输出系统的学习过程。

输入输出,通俗话讲就是进去出来(希望能过审)。

它有多牛逼呢?

它是除了==CPU==和==存储器==计算机硬件系统第三个关键部分。

一.发展情况,了解历史

-

早期阶段

(1)分散连接

(2)CPU与I/O设备串行工作

(4)程序查询方式

(3)I/O设备通过CPU与主存交换消息

-

接口模块和DMA阶段

(1)总线连接

(2)CPU和I/O设备并行

(3)工作:==中断==方式,==DMA==方式。 -

具有通道结构阶段

I/O设备通过通道与主机交换信息。 -

具有I/O处理机的阶段

二.系统组成

是由==I/O软件==和==I/O硬件==组成的。

1.I/O软件

(1)I/O指令

| 操作码 | 命令码 | 设备码 |

|---|

(2)通道指令

- 指出数组的首地址,传送字数,操作命令

- 是通道自身的指令,用来执行I/O操作

2.I/O硬件:包括==接口模块==和==I/O设备==。

三.I/O设备与主机的联系方式

-

I/O设备的编址方式

(1)统一编址:将==I/O地址==看做是==存储器地址==的一部分。

(2)不统一编址:指==I/O地址==和==存储器地址==分开 -

设备寻址:用==设备选择电路==识别是否被选中。

-

传送方式

(1)并行方式(数据同时输送):传送快,但数据线==多==

(2)串行方式(逐位传送):速度慢,但只需==一根==数据线和地址线 -

联络方式

(1)立即响应方式

(2)异步工作采用应答信号联络

(3)同步工作采用同步时标联络 -

连接方式

(1)辐射式:增删困难

(2)总线式:现代被采用

四.I/O设备与主机信息传送的控制方式

- 程序查询

- 程序中断(还在努力编写。。。)。

- DMA方式

作者:RodmaChen

本人博客:https://blog.csdn.net/weixin_46654114

转载说明:务必注明来源,附带本人博客连接。

- 点赞

- 收藏

- 关注作者

评论(0)