计算机组成原理课程设计:复杂模型机

课程设计报告

课程名称: 计算机组成原理

设计题目: 复杂模型机

目 录

1、课程设计任务书 3

1.1设计任务 3

1.2性能指标和设计要求 3

2、本设计的模型机体系结构及功能 4

2.1 模型机的体系结构 5

2.2 模型机所具有的基本功能 5

3、 模型机硬件设计 5

3.1 模型机总体结构设计 5

3.2 模型机的硬件设计 6

3.3 模型机数据通路的设计

4、模型机机器指令系统设计 7

4.1 指令设计 8

4.2 指令格式 9

4.3 指令系统

5、模型机控制器微程序设计 10

5.1 机器指令周期分析 10

5.2 模型机硬件译码电路 11

5.3 微程序流程图设计 12

5.4 微指令格式设计 12

5.5 微指令编码设计 14

5.6 微指令地址及控存存储设计 14

6、模型机功能测试 15

6.1机器指令功能调试 15

6.2整机功能测试 16

7、结论 17

致 谢 18

附 录 18

附录1 18

附录2 20

参考文献 22

1、课程设计任务书

1.1设计任务

- 基本模型机的设计与实现

- 在基本模型机的的基础上设计一台复杂模型机

1.2 性能指标和设计要求

利用所学过的理论知识,特别是微程序设计的思想,设计基于微程序控制器的模型计算机,包括设计相应的硬件平台、机器指令系统和微指令等。设计环境为TD-CMA计算机组成原理教学实验箱、微机,联机软件等。同时设计好基于模型机的测试验证程序,并在设计好的硬件平台上调试通过,以验证所设计的模型机功能的可行性与可靠性。在设计完成的前提下,撰写出符合要求的课程设计说明书并通过设计答辩。

1.基本模型机设计与实现

设计一台简单模型机,在具备基本必要的硬件平台的基础上,进一步要求其机器指令系统至少要包括五条不同类型指令:如一条输入指令(假设助记符为IN),一条加法指令(假设助记符为ADD),一条输出指令(假设助记符为OUT)、一条无条件转移指令(假设助记符为JMP)和一条停机指令(假设助记符为HLT) ; 在设计好的模型机基础上,设计一个进行两个数求和运算的测试验证程序,用以验证模型机功能的可行性与可靠性。

2.在任务1的基础上,增加机器指令系统的功能,设计具有不少于10条机器.指令的复杂指令系统模型机,包含算术逻辑指令、访问内存指令、控制转移指令、输入输出指令、停机指等令。数据的寻址方式采用寄存器直接寻址。利用设计的复杂模型机实现两个数的减法运算并判断差得正负,差为正数则输出A,差为负数则输出B,差为零则输出C。在设计好的模型机基础上,进一步设计-个测试验证程序,验证模型机功能的可行性与可靠性。

3、基本模型机和复杂模型机的CPU数据字长为8位,采用定点补码表示。指令字长为8的整数倍。微指令字长为24位。

2、本设计模型机体系结构及功能

2.1 模型机的体系结构

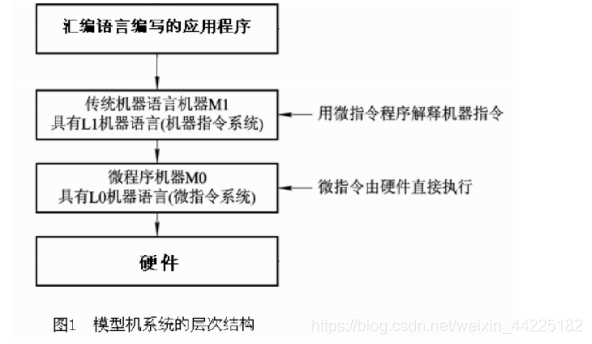

依据计算机系统的层次结构,本次设计的模型机可简化为图1所示的四层结构。我们需要对每一个层次进行设计和实现。

对于最上层的应用程序,本次设计需要设计一个应用程序的测试实例来验证下面三层构成的模型机的功能可行性与可靠性。

2.2模型机所具有的基本功能

本模型机共设计三大类指令,其中包括运算类指令,控制转移类指令,数据传送类指令。运算类指令包含三种运算,算术运算,逻辑运算和移位运算。数据转移类指令包含访问内存指令、输入输出指令等,控制类指令包括停机指令等。实现的功能如:两寄存器的内容相加减,寄存器中数据的移位,外设与寄存器内容交换等多种功能。

3、模型机硬件设计

3.1 模型机总体结构设计

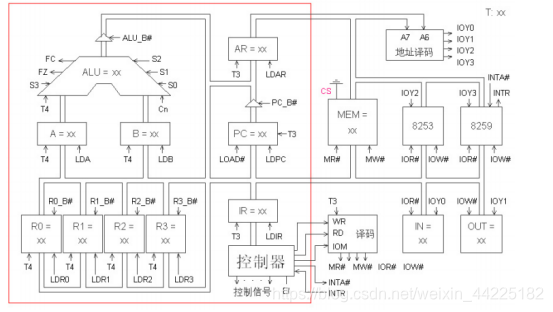

总体结构设计包括确定模型机应具有的基本功能部件以及它们之间的数据通路。根据课堂中所掌握的知识我们可以知道,计算机是由五大部件组成,包括:运算器,控制器,存储器,输入设备和输出设备。所以我们在设计硬件时基于所给出的实验平台选出我们所需要的五大部件(其中包括一些必要的寄存器件)。根据课堂上掌握的只是我们可以知道计算机中总线类型分为: 数据总线,地址总线,控制总线。因此我们在连接线路时脱离不了这三大类型相应的信号(数据信号,地址信号,控制信号)。并且我们根据冯诺依曼机的特点可以知道,计算机的指令在内存中按照其执行顺序存放,并且对于微程序控制器的计算机,控存中必须有固化的微指令。

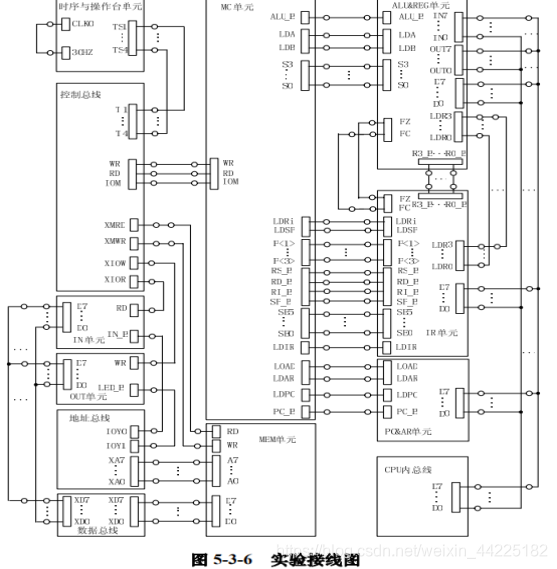

3.2模型机的硬件实现

在本次设计中,硬件的实现基于已给出的实验平台,并根据我们所设计的模型机选择具有控制数据通路开关的必须元器件,通过接插线(各种连线等)将具有控制数据通路的相关引脚进行器件连接,组成所设计的模型机硬件系统(物理机)。

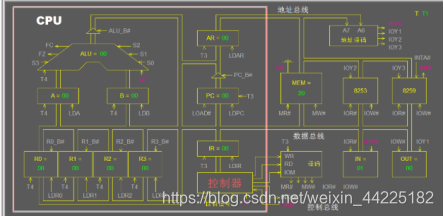

3.3模型机数据通路的设计

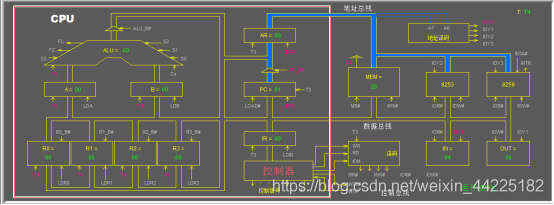

在上面总体结构和硬件实现的基础上,我们组根据各部件之间的逻辑组成关系并综合考虑计算机的速率以及可靠性等各方面因素,设计出合理的数据通路结构。数据通路的不同,执行指令所需要的逻辑操作也就不同,计算机的结构也就不同。在此基础上,在后面的微指令设计阶段,就可以依据数据通路关系确定模型机工作过程中的所有微操作,并进- -步确定微指令格式中的相应微命令。本模型机的硬件实现电路如下图所示:

图中MC单元(控制器)与其右侧的三个单元之间以及ALU®单元间的连线均为本模型机中数据通路的控制开关的引脚,控制相关微命令从而执行对应的微操作。本模型机的数据通路框图:

4、模型机机器指令系统设计

4.1指令设计

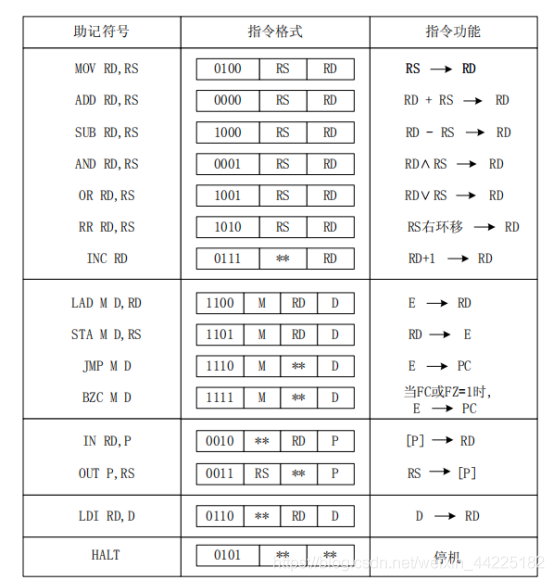

模型机设计三大类指令共十六条,其中包括运算类指令、控制转移类指令,数据传送类指令。运算类指令包含两种运算,算术运算、逻辑运算,设计有5条运算类指令,分别为: ADD、AND、INC、 SUB、OR,所有运算类指令都为单字节,寻址方式采用寄存器直接寻址。控制转移类指令有三条HLT、 JMP、BZC,指令。数据传送类指令有IN、 OUT、 MOV、LDI、 LAD、STA、 PUSH、 POP共6条,用以完成寄存器和寄存器、寄存器和I/0、 寄存器和存储器之间的数据交换,除MOV指令为单字节指令外,其余均为双字节指令。

4.2指令格式

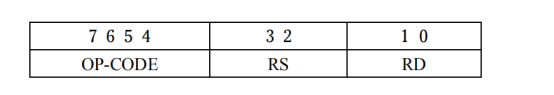

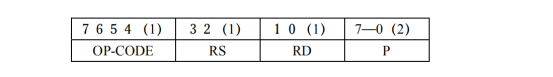

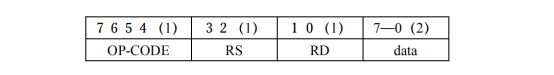

所有单字节指令(ADD、 AND、INC、 SUB、OR、RR、 HLT和MOV)格式如下:

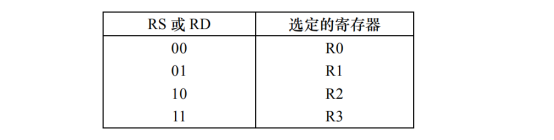

其中,OP-CODE为操作码,RS为源寄存器,RD为目的寄存器,并规定:

IN和OUT的指令格式为:

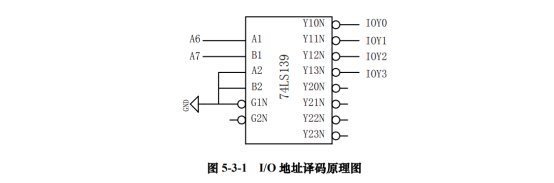

其中括号中的1表示指令的第一字节,2表示指令的第二字节,OP-CODE为操作码, RS为源寄存器,RD为目的寄存器,P为I/O端口号,占用一个字节,系统的I/O地址译码原理见图5-3-1 (在地址总线单元)。

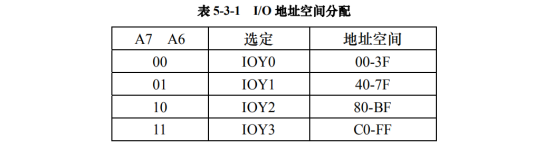

由于用的是地址总线的高两位进行译码,I/O地址空间被分为四个区,如表5-3-1所示:

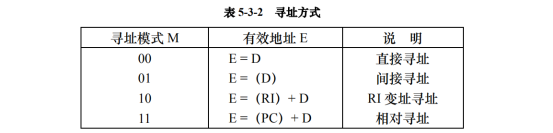

系统设计五种数据寻址方式,即立即、直接、间接、变址和相对寻址,LDI指令为立即寻址,LAD、STA、JMP和BZC指令均具备直接、间接、变址和相对寻址能力。

LDI的指令格式如下,第-字节同前一样,第二字节为立即数。

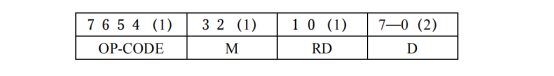

LAD、STA、JMP和BZC指令格式如下。

- 1

其中M为寻址模式,具体见表5-3-2,以R2做为变址寄存器RI。

- 1

4.3指令系统

本模型机共有15条基本指令,表5-3-3列出了各条指令的格式、汇编符号、指令功能。

5、模型机控制器微程序设计

5.1机器指令周期分析

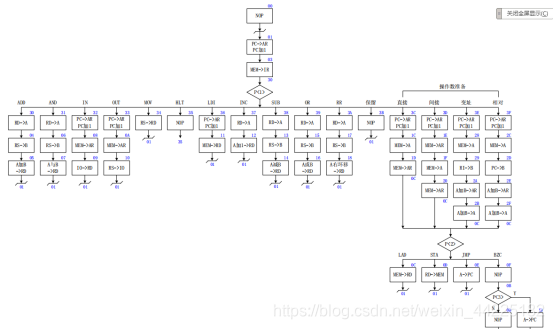

根据课堂所掌握的知识,我们可以知道机器指令周期可以分为两部分:取指周期和执行周期。在本模型机中不同的机器指令取指周期都是相同的,都需要经过两个CPU周期和P<1>测试。其中,两个CPU周期在数据通路.上先后完成PC->AR,PC+1和MEM->IR的控制和传送操作;在P<1>测试阶段,对机器指令的操作码进行测试,确定指令实现的功能。对于执行周期,每个机器指今执行过程互不相同,所经过的CPU周期数以及在不同周期对应的数据通路操作也不尽相同。设计过程中,我们组根据每- -条机器指令所要实现的功能,设计出其在执行过程中每个CPU周期在数据通路上完成的操作,并绘制出它的微程序流程图。

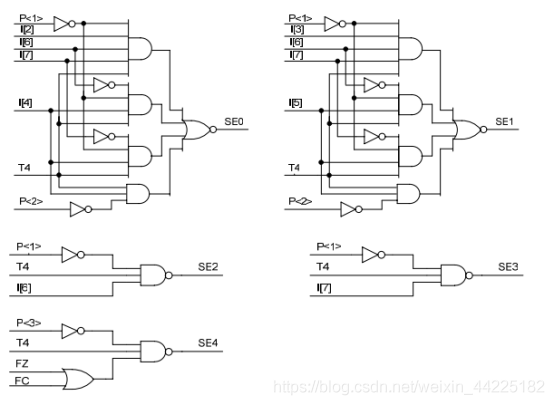

5.2模型机硬件译码电路

和前面的实验相比,复杂模型机实验指令多,寻址方式多,只用一种测试已不能满足设计要求,为此指令译码电路需要重新设计。如图5-3-3所示在IR单元的INS、DEC 中实现。

其中,|[7] ~ |[0]为机器指令的第7位到第0位, T4表示在T4为高电平时有效。本实验用到4个通用寄存器R0~R3,对寄存器的选择是通过指令的第四位,为此还得设计一个寄存器译码电路:

5.3微程序流程图设计

微程序流程图与方框图表示的指令的指令周期是一致的,一个方框是一个CPU周期,-一个CPU周期对应一条为指令。

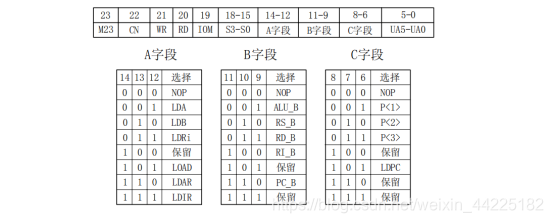

5.4微指令格式设计

①由上述程序流程图可知,本模型机共用到了60条微指令,所以直接微地址需要6位

②控制数据通路开关的为命令共有16种(包括3种P测试),但考虑本机硬件上最大支持24位的微指令,若用直接表示法,微指令字较长, 24位可能不够,因此本模型机采用混合表示法;考虑到后期拓展及同组互斥的性质,将上述的微命令分到A,B,C三个字段中,每个字段长3位。

③模型机中有针对运算器的操作,因此需要5位控制参数CN和S3~S0控制运算器的工作方式

④模型机中有针对主存及外设的操作,所以需要3位微命令I0/M, WR和RD,分别表示针对外设/主存,读操作或写操作。

综上所述,我们所设计的模型机的微指令字长应为23位,但综合考虑到后后期功能的拓展以及设计.上的便捷,所以我们决定将字长拓展至24位。

微指令格式如下所示:

5.5微程序编码设计

微指令中A、B、C三个字段的编码方案如下表:

其中,M23为补充位,无效,置为0;I0M位置0时为主存,置1时为I0外设;WR和RD置1时有效,置0时无效。

- 1

5.6微指令地址及控存存储器设计

首先确定取值过程中两条微指令在控存中地址,以及第二条指令的直接微地址。其次,在此模型机中,所有机器指令执行过程中第一条微指令所在的微地址由P<1>测试前的默认微地址和机器指令操作码经P<1>测试后决定;其次,执行过程中最后-条微指令的直接地址应该设为第-条取值微指令所在的微地址;然后,设置其余微指令所在的微地址,我们组采用的方法为对于每一道微程序,若不存在P<2>和P<3>测试,则入口地址从低到高从上向下为每条微指令分配微地址,因为下一条微指令的微地址即为上一条微指令的直接微地址,若存在P<2>或P<3>测试,则还应通过译码电路来求其后续微地址;最后,分配完微地址后,将所有微指令写入控存对应的位置中。对于控存的要求,控存的容量至少要等于所有微指令的个数,即控存的位数应大于等于直接微地址的位数。

6、模型机功能测试

6.1整机功能调试

本次课程设计一个复杂指令模拟计算机,其硬件系统的组成必须包含CPU、主存、输入输出系统,当然还有连接这些部件的系统总线。CPU又进- -步由运算器和控制器以及各种寄存器等组成。对于微程序控制器的计算机,控制存储器中必须预先固化相应的微指令。依据各部件之间的逻辑组成关系,设计出模型机的总体结构和数据通路。复杂指令模型机硬件连线如下图所示。

复杂模型机数据流向图如下

6.2机器指令功能调试

在本次课程设计中,我们小组一共设计了16条指令,其中DDEC和DAB指令具有递减二、得出两数大小关系的功能。对于DDEC指令,我们是在DEC原指令的基础上修改的。在原来的DEC中,存储在R0中的数据送入ALU单元进行递减操作后,会立马送回R0,在这里我们修改了最后一条微指令,当在ALU单元完成了递减操作后,送入R0,然后又继续送入ALU单元,进行递减操作,最后送入R0,之后再提起下一条指令。

在设计下一条比较两数大小关系指令的时候,我们遇到了非常多的困难。其中在按照地址转移的一个跳转指令遇到了难题。系统无法按照理想的情况跳转到应该去的地方。后面请教了老师和同学,才把问题搞懂。这条指令的格式为DAB A ,B,得出结果:如果A>B,则输出B,A<B,则输出A,若两数相等,则输出C。这条指令的设计我们采取的方案是融合多条指令,合并成一条指令。简而言之,需要先写出多指令的算法,然后把这些多指令的微指令连续的拼接在一起。我们采取的算法是:从IN单元分别输入两个数,分别存储在R0,R1,然后同时送入ALU单元进行相减,根据是否产生借位筛选出一种情况(这里筛选出的是大于),然后将两数还原,再同时送入ALU单元,进行相减操作(注意此时两数的位置发生了交换),进行同样的借位判断,筛选出一种情况,同时另一种情况也就筛选出来了。

7、结论

在本次课程设计中,学会了简单模型机和复杂模型机的设计,同时也对微指令有了更加深刻的了解。在课设初期,我们组先验证简单模型机的工作原理和微指令对程序运行的控制。在第一次验证的原理的时候,总是得不出正确答案。多次验证程序和微指令并确保无误后,检查连线,发现有条线居然忘连了。后面为了保证程序可以正确运行,我们又重新插了一次线,确保无误后,编译并运行程序。最终,终于得出正确结果。之后我们在CMA软件上对程序的每一步进行原理学习,力求搞懂每一步为什么要这样?对于一些难题,我们采取小组讨论和询问同学、老师的办法。最后,我们用了一天的时间完成了简单模型机的验证。在课程设计的第二天,我们开始进行复杂模型机的原理验证,在第一天的教训下,我们组对每一个环节进行了严格的审查,最终仅用了一上午的时间完成了复杂模型机的原理验证。在下午,我们便开始了进行新指令的设计和测试程序的设计。但是期间在微指令这块遇到了一个难题,就是我们的程序只可以单步执行,不可以连续执行。在查找一下午的原因后,我们发现原来是实验箱的问题,并非是程序的问题。在第三天我们的任务便是完成整机测试和编写答辩材料。通过本次课设,自己也是学到了很多,特别是在团队合作方面,为今后的团队工作提供了一定的团队经验。

8、致谢

在本次计算机组成原理课程设计中,还是非常感谢同学们和老师的帮助。在开始的简单模型机的原理论证方面,自己在P测试上面遇到了困难,对其工作原理不是很了解。后来经过同学们一番讲解后,自己才理解了P测试的正确意思。在后面的微指令与程序指令的联系时,开始的时候也是云里雾里,好在当时老师给我指点迷津,这才让我们更快的完成复杂模型机的论证。

9、附录

附录一

DINC指令整机测试代码和微指令集合

$P 00 20;IN R0,00H

$P 01 00

$P 02 30;OUT 40H,R0

$P 03 40

$P 04 70;DDEC R0

$P 05 30;OUT 40H,R0

$P 06 40

$P 07 50;HALT

$M 00 000001 ;NOP

$M 01 006D43 ;PC->AR, PC加1

$M 03 107070 ; MEM->IR, P<1>

$M 04 002405 ; RS->B

$M 05 04B201 ; A加B->RD

$M 06 002407 ; RS->B

$M 07 013201 ; A与B->RD

$M 08 106009 ; MEM->AR

$M 09 183001 ; IO->RD

$M 0A 106010 ; MEM->AR

$M 0B 063201 ;

$M 0C 103001 ; MEM->RD

$M 0D 200601 ; RD->MEM

$M 0E 005341 ; A->PC

$M 0F 0000CB ; NOP, P<3>

$M 10 280401 ; RS->IO

$M 11 103001 ; MEM->RD

$M 12 063238 ; A减1->RD

$M 13 002414 ; RS->B

$M 14 05B201 ; A减B->RD

$M 15 002416 ; RS->B

$M 16 01B201 ; A或B->RD

$M 17 002418 ; RS->B

$M 18 02B201 ; A右环移->RD

$M 1B 005341 ; A->PC

$M 1C 10101D ; MEM->A

$M 1D 10608C ; MEM->AR, P<2>

$M 1E 10601F ; MEM->AR

$M 1F 101020 ; MEM->A

$M 20 10608C ; MEM->AR, P<2>

$M 28 101029 ; MEM->A

$M 29 00282A ; RI->B

$M 2A 04E22B ; A加B->AR

$M 2B 04928C ; A加B->A, P<2>

$M 2C 10102D ; MEM->A

$M 2D 002C2E ; PC->B

$M 2E 04E22F ; A加B->AR

$M 2F 04928C ; A加B->A, P<2>

$M 30 001604 ; RD->A

$M 31 001606 ; RD->A

$M 32 006D48 ; PC->AR, PC加1

$M 33 006D4A ; PC->AR, PC加1

$M 34 003401 ; RS->RD

$M 35 000035 ; NOP

$M 36 006D51 ; PC->AR, PC加1

$M 37 001612 ; RD->A

$M 38 00160B ; RD->A

$M 39 001615 ; RD->A

$M 3A 001617 ; RD->A

$M 3B 000001 ; NOP

$M 3C 006D5C ; PC->AR, PC加1

$M 3D 006D5E ; PC->AR, PC加1

$M 3E 006D68 ; PC->AR, PC加1

$M 3F 006D6C ; PC->AR, PC加1

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

附录二

两数比较大小整机测试代码和对应微指令

$P 00 20;IN R0,00H

$P 01 00

$P 02 21;IN R1,00H

$P 03 00

$P 04 81;SUB R0,R1

$P 05 F0;BZC case1

$P 06 0C

$P 07 62;LDI R2,0AH

$P 08 0A

$P 09 38;OUT 40H,R2

$P 0A 40

$P 0B 50;HALT

$P 0C 01;case1:ADD R1,R0

$P 0D 84;SUB R0,R1

$P 0E F0;BZC case2

$P 0F 15

$P 10 62;LDI R2,0BH

$P 11 0B

$P 12 38;OUT 40H,R2

$P 13 40

$P 14 50;HALT

$P 15 62;LDI R2,0CH

$P 16 0C

$P 17 38;OUT 40H,R2

$P 18 40

$P 19 50;HALT

$M 00 000001 ;NOP

$M 01 006D43 ;PC->AR, PC加1

$M 03 107070 ; MEM->IR, P<1>

$M 04 002405 ; RS->B

$M 05 04B201 ; A加B->RD

$M 06 002407 ; RS->B

$M 07 013201 ; A与B->RD

$M 08 106009 ; MEM->AR

$M 09 183001 ; IO->RD

$M 0A 106010 ; MEM->AR

$M 0B 000001 ; NOP

$M 0C 103001 ; MEM->RD

$M 0D 200601 ; RD->MEM

$M 0E 005341 ; A->PC

$M 0F 0000CB ; NOP, P<3>

$M 10 280401 ; RS->IO

$M 11 103001 ; MEM->RD

$M 12 063201 ; A加1->RD

$M 13 002414 ; RS->B

$M 14 05B201 ; A减B->RD

$M 15 002416 ; RS->B

$M 16 01B201 ; A或B->RD

$M 17 002418 ; RS->B

$M 18 02B201 ; A右环移->RD

$M 1B 005341 ; A->PC

$M 1C 10101D ; MEM->A

$M 1D 10608C ; MEM->AR, P<2>

$M 1E 10601F ; MEM->AR

$M 1F 101020 ; MEM->A

$M 20 10608C ; MEM->AR, P<2>

$M 28 101029 ; MEM->A

$M 29 00282A ; RI->B

$M 2A 04E22B ; A加B->AR

$M 2B 04928C ; A加B->A, P<2>

$M 2C 10102D ; MEM->A

$M 2D 002C2E ; PC->B

$M 2E 04E22F ; A加B->AR

$M 2F 04928C ; A加B->A, P<2>

$M 30 001604 ; RD->A

$M 31 001606 ; RD->A

$M 32 006D48 ; PC->AR, PC加1

$M 33 006D4A ; PC->AR, PC加1

$M 34 003401 ; RS->RD

$M 35 000035 ; NOP

$M 36 006D51 ; PC->AR, PC加1

$M 37 001612 ; RD->A

$M 38 001613 ; RD->A

$M 39 001615 ; RD->A

$M 3A 001617 ; RD->A

$M 3B 000001 ; NOP

$M 3C 006D5C ; PC->AR, PC加1

$M 3D 006D5E ; PC->AR, PC加1

$M 3E 006D68 ; PC->AR, PC加1

$M 3F 006D6C ; PC->AR, PC加1

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

文章来源: haihong.blog.csdn.net,作者:海轰Pro,版权归原作者所有,如需转载,请联系作者。

原文链接:haihong.blog.csdn.net/article/details/113741942

- 点赞

- 收藏

- 关注作者

评论(0)