FPGA开发 Quartus Signaltap的基本使用

【摘要】 一、前言

Signaltap是嵌入式逻辑分析仪,说到嵌入式,很容易让人想起ARM,其实 Signaltap 跟 ARM 没有半毛钱关系。这里的嵌入是嵌到 FPGA 的内部。

如果你用过Signaltap,就会发现,每次都要综合整个工程,再下载代码,然后才可以使用Signaltap,这说明了 Signaltap 是由一些逻辑电路组成,而不是仿真。

请不要把 Sign...

一、前言

Signaltap是嵌入式逻辑分析仪,说到嵌入式,很容易让人想起ARM,其实 Signaltap 跟 ARM 没有半毛钱关系。这里的嵌入是嵌到 FPGA 的内部。

如果你用过Signaltap,就会发现,每次都要综合整个工程,再下载代码,然后才可以使用Signaltap,这说明了 Signaltap 是由一些逻辑电路组成,而不是仿真。

请不要把 Signaltap 和 Modelsim 混为一谈(如果是一样的话,就不用起两个名字了),就算两个软件的界面上的波形很像。

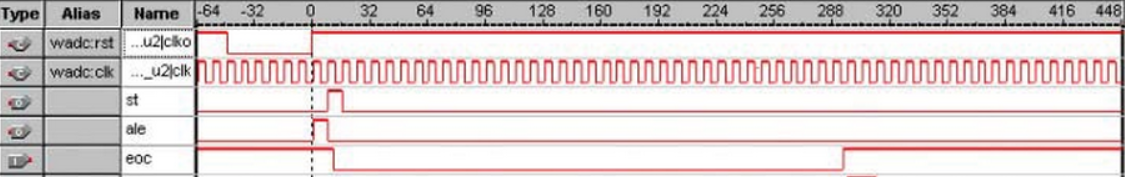

以下是 Signaltap 界面上的波形(代表实际的波形)。

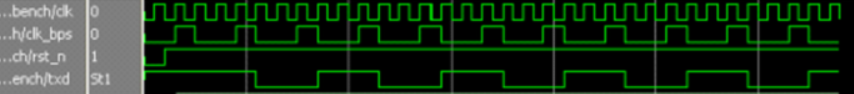

以下是 Modelsim 界面上的波形(代表仿真的波形)

二、基本操作

首先,要确保你的 project 能成功综合,并且所消耗的资源不能为0。

然后在 Quartus 界面下,点开 Tools 菜单,打开SIgnaltap。

文章来源: yetingyun.blog.csdn.net,作者:叶庭云,版权归原作者所有,如需转载,请联系作者。

原文链接:yetingyun.blog.csdn.net/article/details/118388639

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)