TMS320C6678+Kintex-7视频采集处理案例-汇总篇

【摘要】 目录1 C6678+Kintex-7平台简介2 DSP+FPGA架构优势3 视频采集处理方案3.1 SDI视频采集处理3.2 PAL视频采集处理(4路D1)3.3 HDMI视频采集处理3.4 CameraLink视频采集处理需要案例源码请在文章下方留言联系。O(∩_∩)O谢谢。1 C6678+Kintex-7平台简介 在高速图像处理领域,TMS320C6678 与 Kin...

在高速图像处理领域,TMS320C6678 与 Kintex-7进行搭配的DSP+FPGA架构堪称经典中经典,前无古人后无来者。TMS320C6678+Kintex-7架构大范围使用已经超过了8年时间,使用者数量也越来越多,但远没有达到鼎盛阶段!

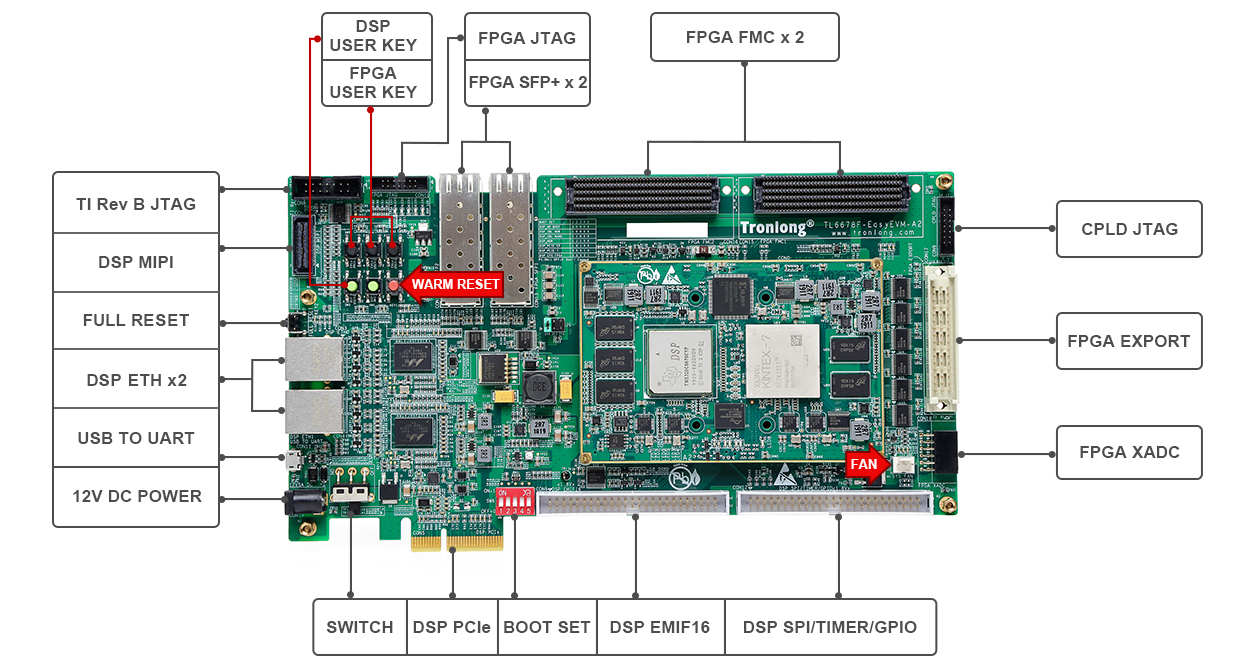

创龙科技 (Tronlong) 结合TI KeyStone系列多核架构TMS320C6678 DSP以及Xilinx Kintex-7 FPGA设计的TL6678F-EasyEVM评估板,是一款DSP+FPGA高速大数据采集处理平台,由核心板与底板组成。核心板内部DSP与FPGA通过SRIO、EMIF16、I2C通信总线连接。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。评估板接口资源丰富,引出PCIe、千兆网口、FMC、SFP+等高速通信接口,方便用户快速进行产品方案评估与技术预研。

TL6678F-EasyEVM评估板通过FMC高速接口,可接入CameraLink、SDI、PAL、HDMI等视频采集模块,并基于各个模块提供了DSP+FPGA视频采集处理综合案例,同时提供技术支持服务。

图 1 TL6678F-EasyEVM评估板

2 DSP+FPGA架构优势

高性能的算法处理,使用硬件描述语言去编写算法的话,复杂程度高,工作量大,不易调试,产品的开发周期将非常长。这时,如果为系统添加专为算法而生的DSP的话,将会事半功倍。

众所周知,DSP有专门为数字信号处理所设计的指令集和流水线,可以方便高效的执行浮点数和复数运算等,这样我们的理论算法就可以很方便的移植到实际的工程中,可以有效的缩短产品的开发周期。

DSP+FPGA的架构,可以把FPGA的高速采集和DSP的高性能算法处理完美结合。这种高度平衡的特性集合使其非常适合各种高性能嵌入式应用场合,如:

n 视频追踪

n 图像处理

n 软件无线电

n 雷达探测

n 光电探测

n 水下探测

n 定位导航

3 视频采集处理方案

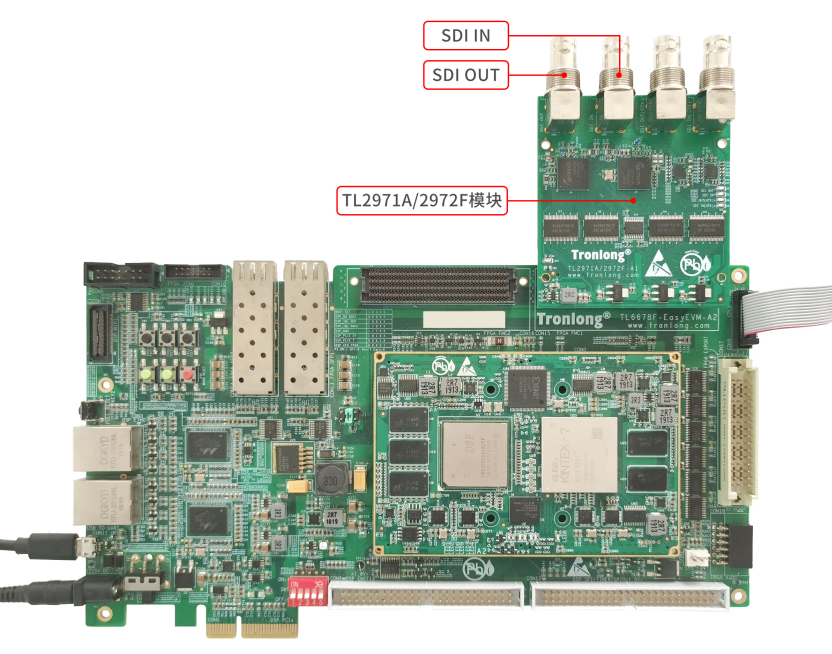

3.1 SDI视频采集处理

Kintex-7 FPGA通过使用Video In to AXI4-Stream IP核,将SDI视频模块TL2971A/2972F的SDI IN接口输入的1080P60的视频采集进来,并通过VDMA缓存到DDR,最后通过AXI4-Stream to Video Out IP核将视频从模块的SDI OUT接口输出显示。其中VDMA通过Microblaze配置。

图像数据亦可通过SRIO高速总线传输到TMS320C6678 DSP进行算法处理,并返回处理结果。

图 2

图 3 硬件连接

需要案例源码请在文章下方留言联系。O(∩_∩)O谢谢。

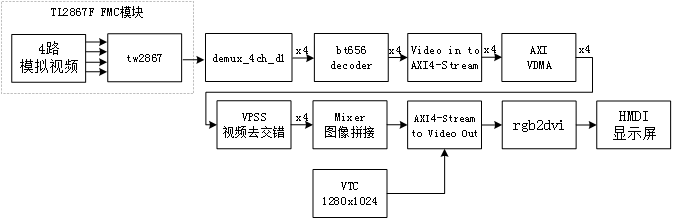

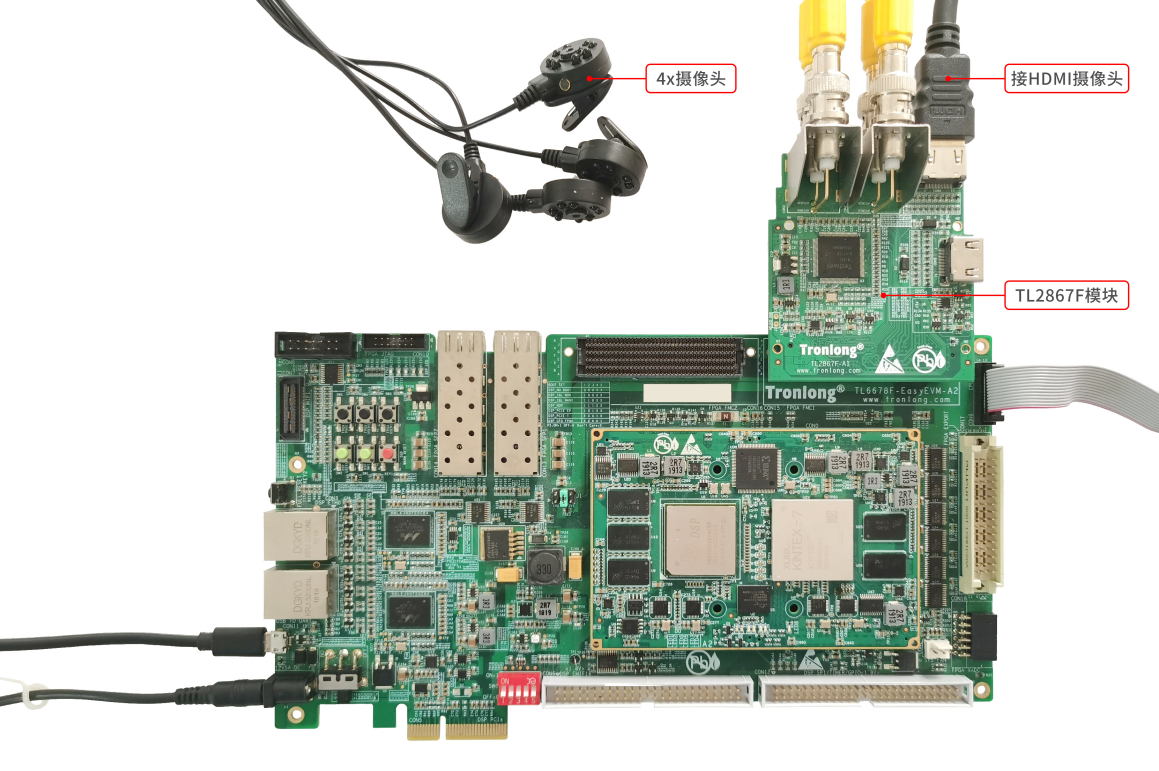

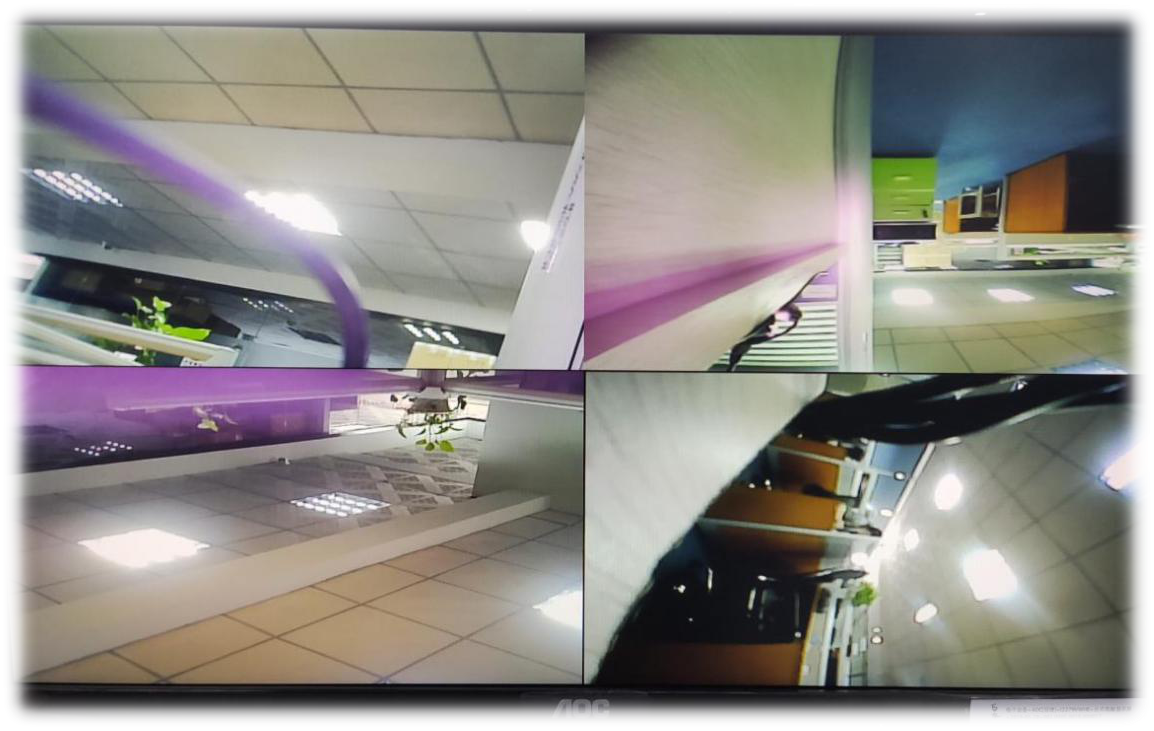

3.2 PAL视频采集处理(4路D1)

在Kintex-7 FPGA上搭建MicroBlaze软核,并由MicroBlaze配置PAL视频模块TL2867F和各IP核,将模块输出的一路4通道D1时分复用的复合视频,拆分成4路独立的BT656嵌入式同步视频,再将4路视频进行BT656解码分离出同步信号和像素数据。使用VDMA IP缓存到内存设备上,通过VPSS IP将4路图像进行去交错,然后由Mixer IP将四路图像拼接起来,通过rgb2dvi逻辑模块,将RGB视频信号转换为DVI视频信号,最后通过模块的HDMI1接口输出显示到显示器。支持PAL制式(分辨率为720x576)视频输入,输出显示分辨率为1280x1024。

图像数据亦可通过SRIO高速总线传输到TMS320C6678 DSP进行算法处理,并返回处理结果。

图 4

图 5

图 6 硬件连接

图 7

需要案例源码请在文章下方留言联系。O(∩_∩)O谢谢。

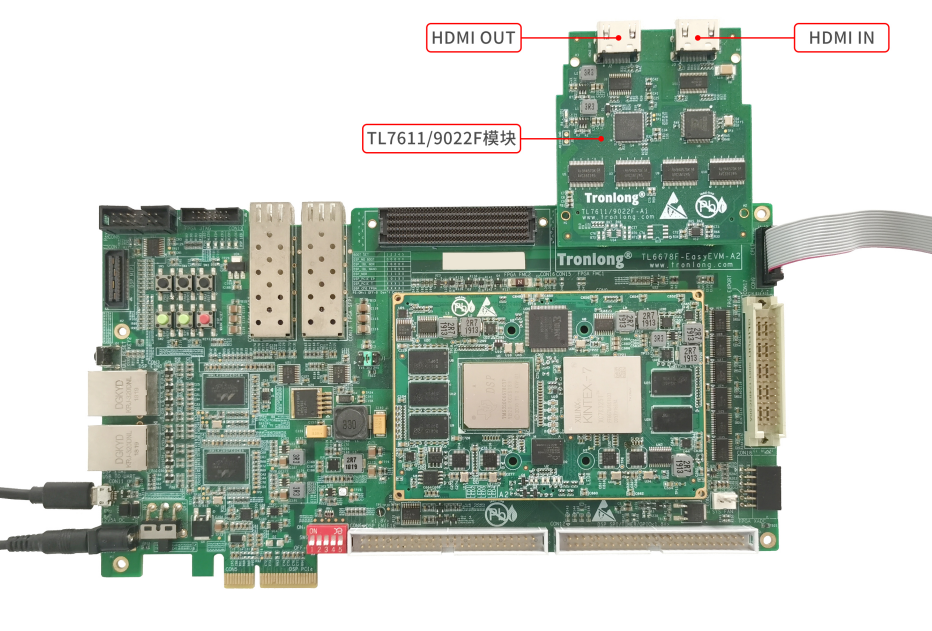

3.3 HDMI视频采集处理

Kintex-7 FPGA使用Video In to AXI4-Stream IP核,通过HDMI视频采集模块TL7611/9022F的HDMI IN接口将1080P60视频采集进来,并通过VDMA缓存到DDR,最后通过AXI4-Stream to Video Out IP核将视频从模块的HDMI OUT接口输出显示。其中VDMA IP核,HDMI OUT芯片(SIL9022)和HDMI IN芯片(ADV7611)通过MicroBlaze运行裸机程序进行配置。

图像数据亦可通过SRIO高速总线传输到TMS320C6678 DSP进行算法处理,并返回处理结果。

图 8

图 9 硬件连接

源码请直接查看本文【 5源码、资料下载】进行下载。

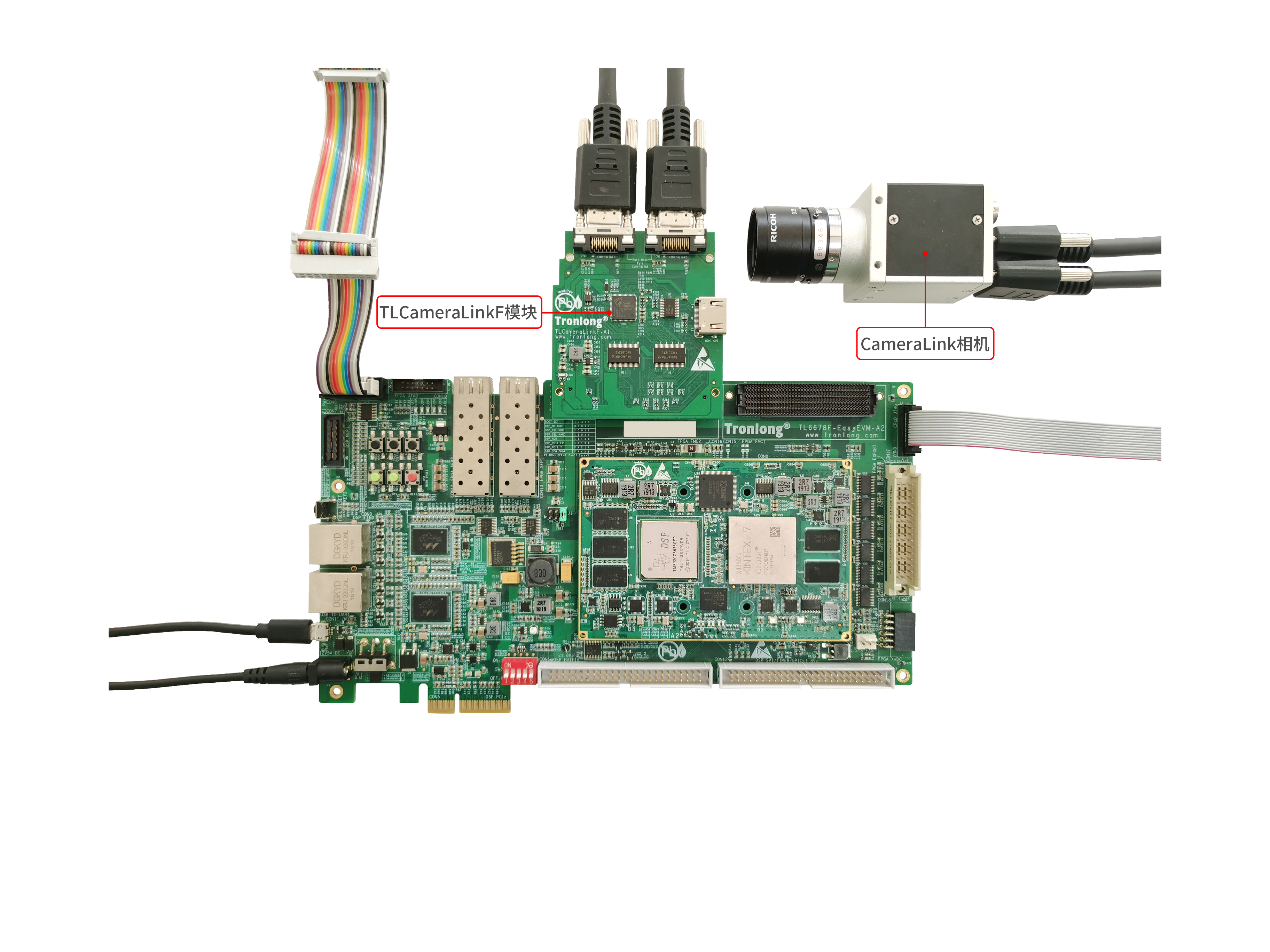

3.4 CameraLink视频采集处理

基于CameraLink的DSP+FPGA视频采集处理综合案例,将于下个月发布,欢迎咨询。

图 10

图 11 硬件连接

需要案例源码请在文章下方留言联系。O(∩_∩)O谢谢。

【声明】本内容来自华为云开发者社区博主,不代表华为云及华为云开发者社区的观点和立场。转载时必须标注文章的来源(华为云社区)、文章链接、文章作者等基本信息,否则作者和本社区有权追究责任。如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)