FPGA的设计艺术(8)最佳的FPGA开发实践之严格遵循过程

前言

本文首发自:易百纳技术社区,链接:FPGA的设计艺术(8)最佳的FPGA开发实践之严格遵循过程

对于很多人来说,FPGA的开发很随意,要实现一个什么功能,在大脑里随便思考一下,就开始写逻辑,“天马行空”,水平看起来很高的样子。你若问他FPGA开发的流程,他也知道,但也仅仅局限于理论上的东西,从来不去实践,或没有这个习惯,或环境使然(例如,没人给你这个时间,我要求了,你就得立即给我干,不要让我看到你在看手册或者思考,这都是很死板的表现)。这种方式在高校尤为常见,或者不太正规的公司,功能的实现全靠导师口述,你给我实现个什么什么,很简单,这么做,那么做?

毫不夸张的说,这种方式让设计的质量几乎得不到保证,再加上高校学生的逻辑设计水平,参差不齐,或者说大多数都是初学者,上来就搞一个高大上的主题,这让逻辑设计的质量得不到保证,上来就干,看起来很牛,但最后逻辑的调试上花了很长的时间,逻辑的功能正确性得不到保障,更别提什么稳定性了!

不说太多了,下面给出一套宇宙通用开发实践准则,这套下来,可见减少FPGA设计错误的可能性,减少常见错误并可以节省FPGA开发过程中的人工成本,并在大型设计中优势更加显著。

从设计的过程中,规避大量的逻辑问题,让调试更轻松,让功能更稳定,产品质量更可靠。

如何花费更少的时间去调试?

长期以来,过程在软件领域已广为人知。几十年。问题在于某些流程人员使流程变得如此繁琐,以至于设计工程师不惜一切代价避免并规避了该流程。这很麻烦,因为过程是确保复杂系统中质量(无缺陷)设计的唯一方法。

严格遵循过程,能留给工程师更多的思考时间,与同行讨论设计,然后采取行动。很多工程师都跳过了“思考和讨论”的步骤。

为什么使用过程?

计算机最初用于执行计算。为了提高效率,我们发明了机械计算器。进一步的发明产生了具有硬连线算法的电子计算器。需要一种新算法以物理方式重新连接系统。这仅允许使用简单算法。

接下来是软件的发明。将算法与硬件分开。就硬件而言,软件的复杂性非常高(一块电路板可能有10,000个节点,而一个软件应用程序可能有数百万行代码)。我们认识到在高度复杂的系统中发现缺陷的困难,并开发了一种过程来确保复杂的系统组件(软件)的质量。

然后,可编程逻辑(FPGA)将数字设计与物理硬件分开。数字设计的复杂性与软件相当,这意味着您无法完全测试FPGA设计。我们需要遵循一个流程来确保复杂系统组件(软件和FPGA)的质量。产品测试仅验证已测试的功能。它不能详尽地测试潜在的缺陷。您无法在数字设计或软件程序中测试质量。此外,过程减少了成本,进度和技术性能的可变性。

流程不是思考的替代品,也不是脱离程序现实的方法。项目负责人必须知道何时以及为何偏离过程。该过程不会替代领域知识;它不能代替熟练,有干劲的工程师。

需要多少过程?

所需的过程数量主要取决于故障的成本。丢失的视频帧可能不会被注意到。电话掉线会打扰客户,并对您的品牌产生不利影响。潜在的安全系统漏洞可能会带来严重的经济后果。飞机上不受控制的飞行控制表面是不可接受的。

该过程必须为您的设计团队增加价值,并且必须适合您的产品。

最小的过程

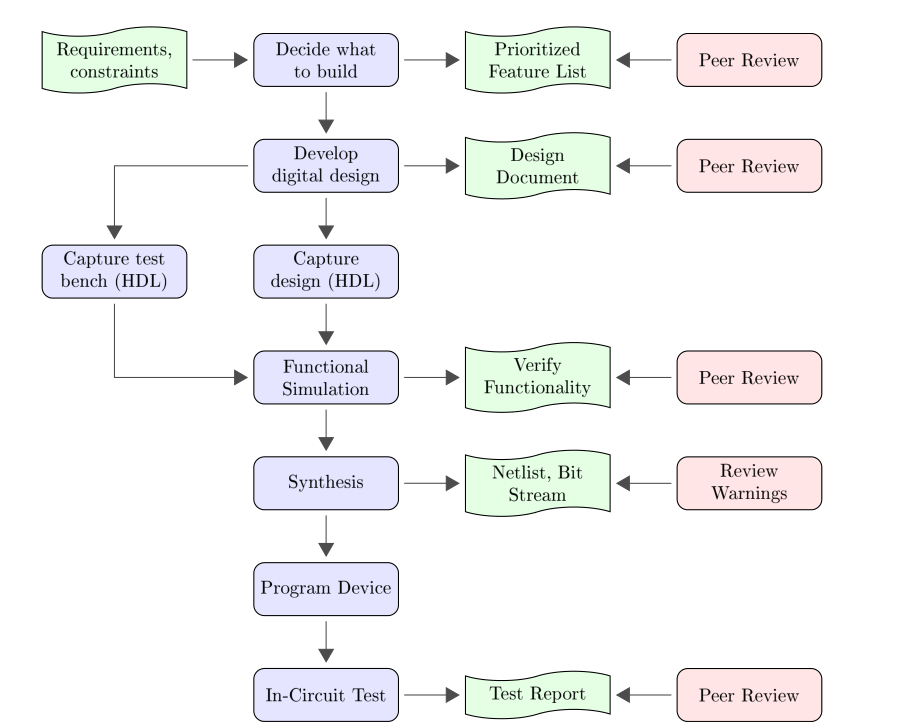

大部分过程描述标准取决于系统的安全重要性,允许不同级别的过程。本节描述了针对非安全关键行业的FPGA开发的最低流程,如图1.1所示。

明确需求

我们可以合理地确定项目的要求会在程序中的某个时候发生变化。输出功能列表有利于两件事:避免由于对构建内容的误解而导致需求变更,并且可以帮助我们确定首先要进行的工作。

注:此步骤需要同行评审;

数字设计方案

在尝试使用硬件描述语言(HDL)捕获数字设计之前,必须对其进行良好定义。记录的详细程度值得商榷;但是,如果无法用时序图,框图和文本描述设计,那么如何期望使用HDL准确地描述设计呢?对设计进行记录是确保他人(包括您的未来版本)6能够快速了解设计的关键。任何不附带文档的设计都是不可接受的。

注:此步骤需要同行评审;

逻辑设计

如果可能的话,不同的工程师都应该掌握设计和测试平台,以免对需求的误解不会同时存在。 与作者,1个或2个高级工程师和1个或2个初级工程师进行代码检查有助于确保代码与设计相匹配,并培训经验不足的工程师。

功能仿真

即使进行最简单的数字设计,也将从功能仿真中受益,从而可以预测系统内的行为。开发良好的设计和仿真实践可以在以后的道路上节省时间。HDL仿真在验证设计时是非常有价值的。它不应该被用作辅助设计过程的拐杖。不要创建一个设计的粗略草案,然后反复仿真和修改,直到它工作,因为这可能会导致缺乏对如何以及为什么它工作的理解。

板上验证

上板验证的目的是确保设计满足所有要求。从FPGA的角度来看,我们想验证模块仿真的输出和在FPGA中实例化的模块对于给定的输入是否匹配。所有要求都必须具有综合后或布局和布线(PAR)后测试。

版本控制

有一些问题可能会给产品团队增加很大的压力。

- 我们提供了哪个版本的软件或FPGA?

- 您有失踪文件的副本吗?

- 您使用哪个文件?

- 您是否覆盖了我的更改?

- 我可以还原文件的早期版本吗?

- 使用哪个版本的工具来实施设计?

修订控制系统创建一个包含每个文件的每个版本的数据库,如果有效地使用它,则可以避免大多数此类问题。

在FPGA设计中,故事的源头远不止于源代码。修订控制系统提供了一种纪律严明的文档化方法来捕获关键设计工件。

两个优秀的开源版本控制系统是Apache Subversion和Concurrent Versions System(CVS)。

编码指南:简短的技术组合,可最大程度地减少错误

编码指南是一些技术的简短集合,这些技术共同作用以最大程度地减少错误。 HDL编码指南旨在由设计团队根据适当的工程判断来执行。不需要所有FPGA代码严格遵守。主要目的是降低逻辑错误的可能性并增强设计人员之间的可移植性。

设计人员的首要任务应该是遵循制造商推荐的FPGA HDL编码风格。制造商编码指南可从其网站上轻松获得。两个示例是《 Altera内部存储器(RAM和ROM)用户指南》 和Xilinx综合与仿真设计指南。

以下示例VHDL编码准则摘录自Intuitive Research and Technology Corporation的VHDL编码准则。

-

泛型不应具有默认值,除非在设计的顶层。

-

不要使用IEEE std_logic_arith,signed 或 unsigned 库。使用ieee.numeric_std库并声明signed 或 unsigned的信号。

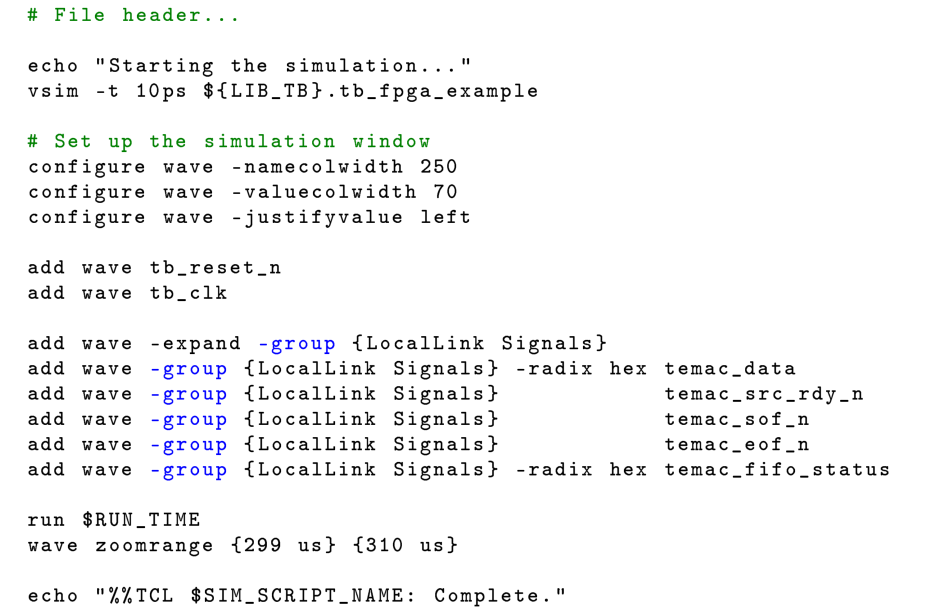

TCL脚本自动化或如何节省时间?

编写工具控制语言(TCL)脚本的目的是使尽可能多的步骤自动化。脚本是关键设计工件,必须在版本控制系统中。以下段落描述了一些好处。

-

在计算机之间的可移植性:综合脚本可以在综合工具中设置大量的后台开关和按钮,以确保设计将独立于主机进行仿真或综合;

-

记住所有步骤:脚本必须具有所有仿真或综合步骤。该脚本捕获有关设置的知识。这可以确保工程师(无论是现在还是几年后)都不会花费时间来调试由于缺少类型的问题而导致的不存在的问题。当您不记得如何将项目组合在一起时,这可以在几个月(或几年)内显着减轻维护工作的负担。

-

自动执行版本更新:脚本可以自动将主机计算机的日期和时间插入FPGA源中,以提供一致的版本寄存器。这避免了烦人的问题,FPGA中的哪个bitstream? 。

-

速度:运行脚本通常比输入(或单击)命令要快得多。这样每小时可以节省几分钟。

下面是一个仿真脚本的部分示例:

总而言之,能用脚本自动化的就不要手动操作。

总结

本文叙述的这套减少调试时间的办法,换句话说就是严格遵循过程来进行项目开发。不同的场景要定不同复杂程度的开发过程,上述还只是一个最小的或者说最简化的过程,可以自我审视下,在开发的过程中,我们是否严格遵循了过程?

我们对没有遵循过程的开发是否抱怨过,这都是谁做的开发,一点文档也没留下,还要看他的代码,还不如我自己重新弄?如果你有过这样的抱怨,那就要重视起来了,每个过程都要有输出!正如文章中所说:任何不附带文档的设计都是不可接受的。 或者英文表达是不是更加掷地有声:

Any design not accompanied by documentation is not acceptable.

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/114710492

- 点赞

- 收藏

- 关注作者

评论(0)